前回、MicroBlazeコアを搭載したHW設計の「バリデーション」までやってノーエラーでした。その余勢をかって今回はSWなどと目論んでいましたがいけません。SW側に「輸出」する最後の段になってエラー発覚。チュートリアル通りにやっているつもりなのに何がいけないの?FPGA素人の忘却力の年寄は大慌てなんであります。

※かえらざるMOS回路 投稿順 INDEX

※Digilent CMOD S7のマニュアルは以下のページにあります。

なお、CMOD S7搭載のFPGAは「多分、お求めやすい」XC7S25-1CSGA225Cです。

※実習には AMD社(Xilinx) Vivado 2023.2 を使用させていただいております。

参照しているチュートリアル

Digilent社の以下のチュートリアル文書を参照して実習しております。この文書は当方が使用しているCMOD S7ボードを含む各種のボードの「AND」とったところの解説です。各種ボードにより異なる「コマケーところ」があるので、そういうところは使用者が「よく考えて」補ってやらねばなりませぬ。今回トラブったところも、結局、前回ちょっと「怪しい」設定をしてしまっていた部分でした。

Using the Simulator Getting Started with Vivado and Vitis for Baremetal Software Projects

HDLラッパからイクスポート

IPを使ったブロック・デザインのバリデーション完了後、SW設計に移行する前にやらねばならないステップは以下です。

-

- HDLラッパ(HDLのソース)を生成

- プロジェクトの合成、インプリ、そしてビットストリーム生成

- プロジェクトのイクスポート(VivadoからVitis用)

チュートリアルに書かれている通りに実習しているのだから、「一撃で通り過ぎる」つもりでいたですが、お約束通りにトラブリました。途中までは順調だったのよ~。

-

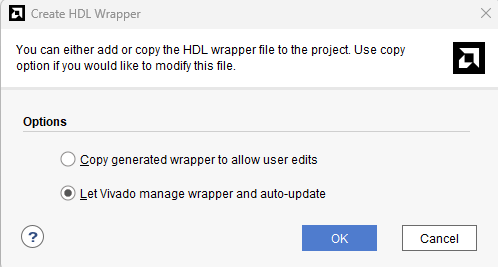

- Create an HDL Wrapper

このステップは、ブロック(IPの箱)で描かれた設計の上にHDLのソースコードを被せるプロセスのようです。みるとブロックの下にもHDLソースが出来ていたので、ブロックの上下にHDLソースを生成し、実際に論理合成できるようにするための準備作業みたいです。今回はVerilog使っているので、.v拡張子のファイルが生成されます。

オプション聞かれましたが、チュートリアルでは「auto-update 推奨」だったのでそちらを選択。お楽が一番。

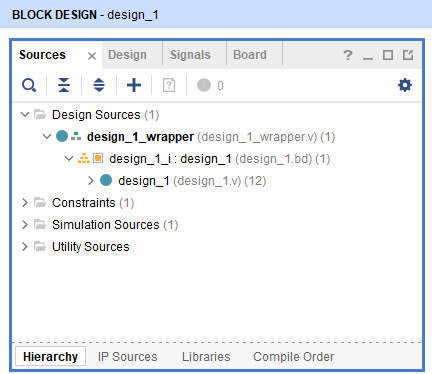

ラッパジェネレーション後のプロジェクト階層の様子が以下に。オレンジアイコンのところがブロックデザイン部分で、その上下に緑のグリグリのVerilogソースが生成されてます。

一応、ソース内部を眺めてみると、ブロックデザイン部分をモジュールとして呼び出すようになってます。また入出力バッファなども結合してますが、なんかやたら多いんでないかい?

-

- SynthesisとImplementation

何度か既にやっているSynthesisとImplementationを実施。特に問題なくSuccessfullyでできました。なお、チュートリアルにはこのプロセスに5分から60分くらいかかるかも知れないと書かれていたですが、当方では約2分ほどで完了。いい感じ。

-

- Generate Bitstream

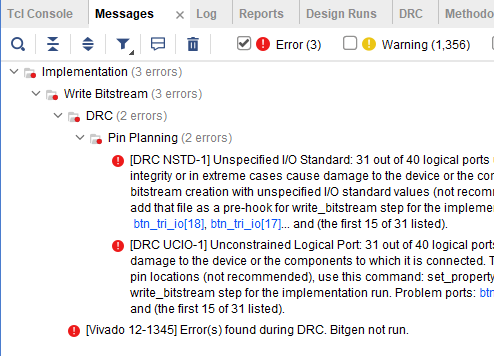

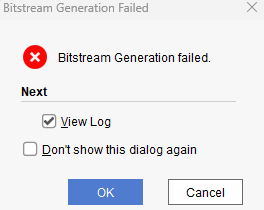

さて上記の「成功」を受けてビットストリームに落とそうとして挫折。こんな感じです。

Bitgenが走らんかったというのは、直接のエラー原因ですが、それはビットストリームが出来てないからです。要は上の2つが原因であろうと。しかしダラダラ書かれているエラーメッセージ読んでもFPGA素人にはサッパリっす。でもま、IOポートの問題であり、そして胸に手を当てて考えると前回その部分に「怪しい」処置を施しておった覚えがあるのであります。それに先ほどのラッパソースに使ってもいないIOポート多数が列挙されていたのも気になるし。。。

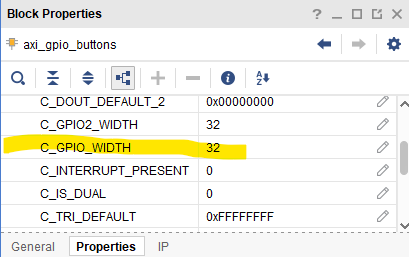

前回気になっていた入力ボタンの「手動設定部分」を確かめてみました。

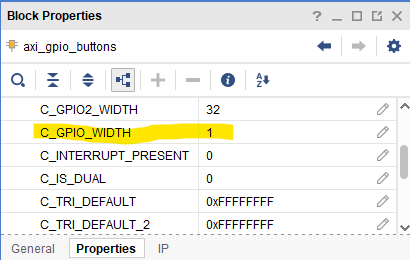

GPIO2ではなく、GPIOというIPで1ビットを選択したつもりなのですが、プロパティを確かめると32になってました。これはイケないということで変更。

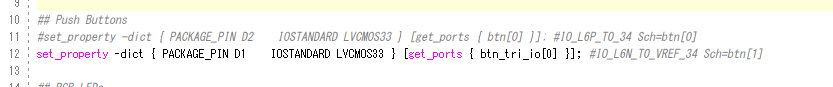

また、前回、制約ファイルを手で修正した部分も気になっていたので、以下のように変更。

上記を変更し、セーブした後、ブロックデザインのバリデーション、論理合成、インプリメンテーションとやりなおし、ビットストリーム生成、どうよ。

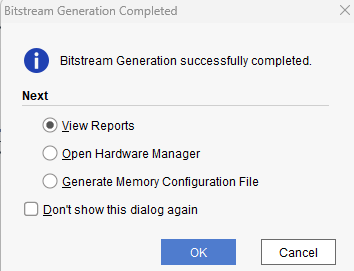

ビットストリーム、successfully completedと。これで「輸出」のステップに進めますな。

ラッパのVerilogソースを見てみると、最初やたら数が並んでいたIOセルらしきものが綺麗サッパリ消滅し、入力ボタン用の1個だけになってました。やっぱ、怪しいソースは通らんぞなもし。

なお、今回生成のデザイン、MicroBlazeコアを含むのですが、使用はLUT 1649個、BRAM8個だそうです。CMOD S7搭載のXC7S25-1CSGA225Cは、

-

- LUT 23360個

- BRAM 18Kb x 90個 + 36kb x 10個

ということみたいなので、まだまだ余裕?知らんけど。

-

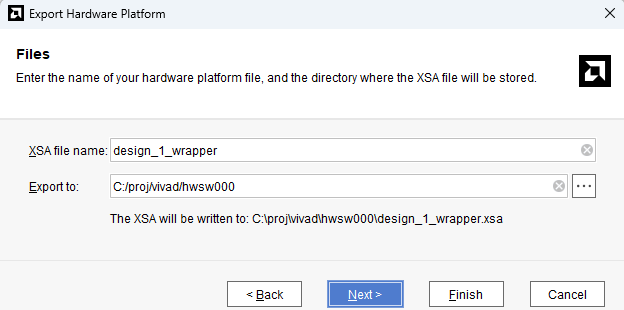

- Export

ビットストリームが出来てしまえば、Exportのプロセスは簡単でした。一応ステップを踏むと。

チュートリアルでは最初に選択あるのですが、当方使用のVivado 2023.2では、最初のウインドウでは選択なしだと。

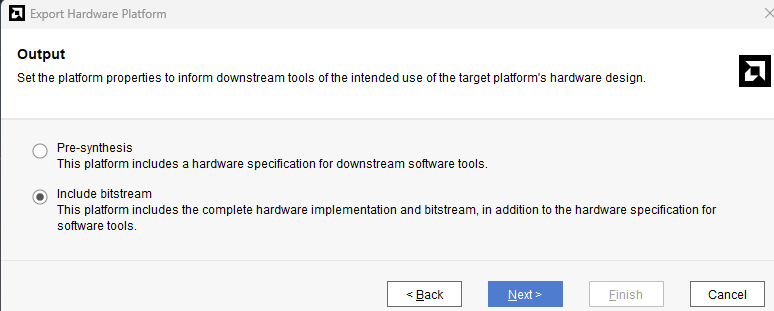

今回は include bitstream を選択。

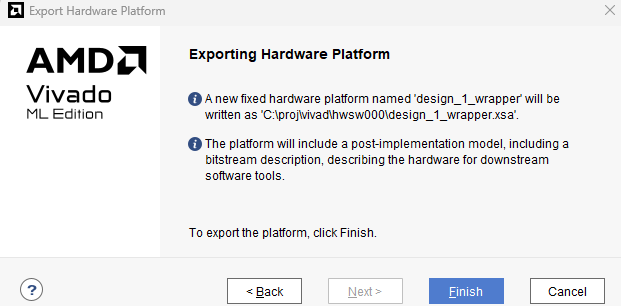

最後にFinishボタンを押せば、xsaなる拡張子のファイルが出来上がります。サイズ的には104kバイト。

ようやく、VivadoからVitisへ行けるみたい。