アナログ素人老人がLTspice配下のExample内Educationalフォルダ所蔵の回路図を巡回中。今回は「ビヘイビアな」原理回路のデモです。PLLつかったFSK復調回路っす。本サイトでもPLL、何度か練習している気がしますが、デモ回路の手際の良さに素人老人はついてイケません。まあ雰囲気だけ。いいのかそれで?

※「SPICEの小瓶」投稿順インデックスはこちら

※アナログデバイセズ社のLTspiceのガイド、ヒント、便利な情報については以下へ。https://www.analog.com/jp/resources/design-tools-and-calculators/ltspice-simulator/ltspice-recommended-reading-list.html

PLL(フェーズ・ロック・ループ)

アナログ素人老人も懲りずにアチコチのシリーズでPLLを何度も練習しております。まずは現物IC、定番で古典的なCD4096を使った練習、3回に渡って各部を舐めてます。

定番回路のたしなみ(19) CD4046でPLL(フェーズロックドループ)その1

定番回路のたしなみ(20) CD4046でPLL(フェーズロックドループ)その2

定番回路のたしなみ(21) CD4046でPLL(フェーズロックドループ)その3

また、アナデバ様のIC、AD654を使って逓倍回路を作る件も3回にわたってます。

お手軽ツールに今更学ぶアナログ(143) PLL実習の前準備、AD654再び

お手軽ツールで今更学ぶアナログ(144) AD654にXOR1個つなげてPLLじゃ

お手軽ツールで今更学ぶアナログ(145) 前回回路を改造、16逓倍PLLじゃ、ホントか?

それどころか、本シリーズでも今回同様なビヘイビアなエレメントを使い、周波数倍周器を練習してます(これはPLLではないけれども。)

SPICEの小瓶(36) BVエレメントで、ビヘイビアな周波数倍周器を

PLL.asc

今回動かしてみるEducationalフォルダ所蔵の回路は PLL.asc です。ビヘイビアなPLL回路が中核となっているデモですが、回路全体としては、

FSK変復調のデモ

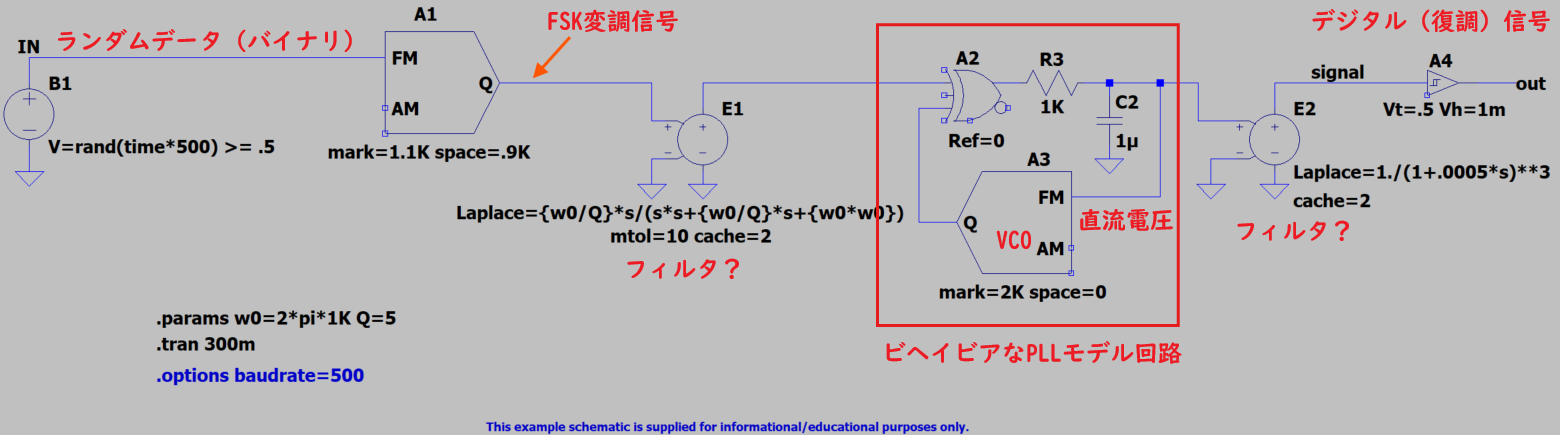

です。デモの回路図とその上に素人老人のコメントを重ねたものが以下に。

赤枠内が、PLL(ビヘイビアだけれども)の「原理回路」っす。左のB1からやってくるバイナリ(デジタル)なランダムデータ列を、FSK変調(これまたビヘイビアなコンポーネント)したアナログ信号に仕立ててPLL通し、そしてデジタルビット列へと復調する回路モデルです。

電圧制御電圧源を駆使してフィルタしているみたいですが、素人老人はLaplaceの文字が見えた時点で見て見ぬフリです。さらっと?こういう回路を描ける中の人は凄いな、とただただ関心。

シミュレーション結果

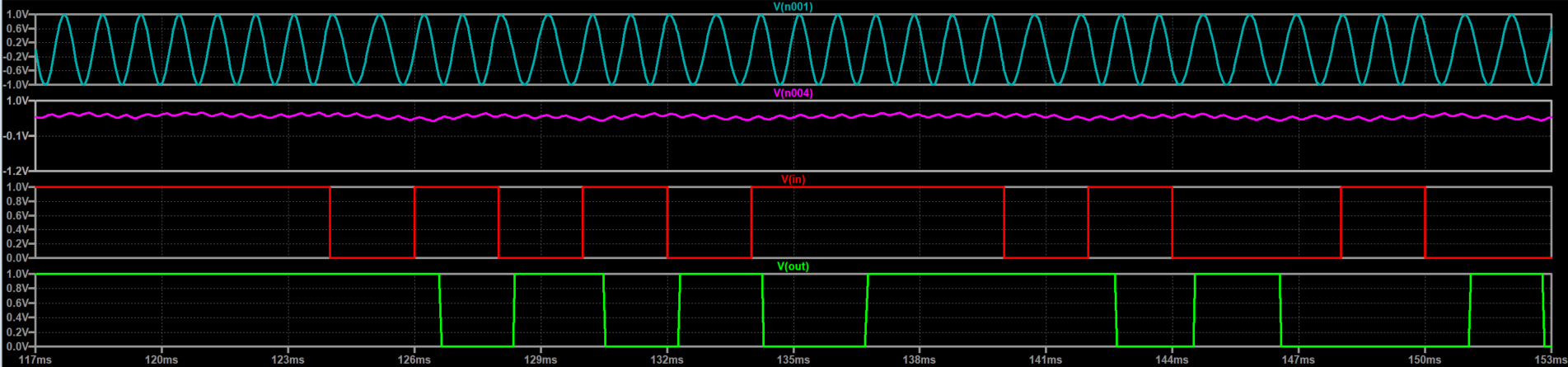

雰囲気分かった気がしたので(実際は何も分かっちゃいないのですが)、シミュレーション結果が以下に。

デモ・ファイルそのままだと、下2つの「デジタル信号」のペインで、全体の入力と出力のみ表示されます。素人老人はそれではPLLの有難みが感じられないので、FSKの変調信号のところと、それをPLLで直流電圧信号に変換しているところも上2つのペインに表示してみました。

まあ「原理回路」ってことだけれども、鋭いよ、惚れてまうなあ。