前回、定番のPLL-IC、CD4046を使い始めてみました。初回の前回はPLLの中心要素VCO(電圧制御発振器)の特性を眺めてみました。2回目の今回は、VCO出力に分周器などかませず1:1で外部からの入力信号にフェーズ・ロックを試みたいとおもいます。IC内蔵の位相比較器と外付けLPF(ローパスフィルタ)を追加。

※「定番回路のたしなみ」投稿順Indexはこちら

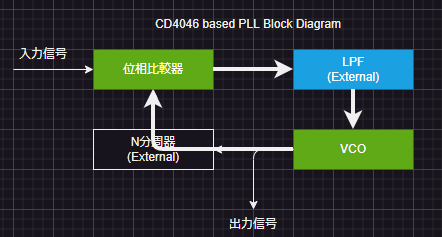

今回実験する構成

今回は以下のような「ループ」を回して入力信号に対して位相固定で周波数は1:1の出力信号を得たいと思います。周波数をN逓倍するときに使用する外付けのN分周器は使用せず、VCO出力を位相比較器と直結します。やることと言えば外付けLPF(RCローパスフィルタ)の定数を決めるくらいです。

CD4046

今回実験に使っているCD4046はTIの製品であります。製品ページが以下に。古い製品の筈ですが、いまだに「アクティブ」だと。定番に違いないっす。

CD4046B CMOS マイクロパワー・フェーズ・ロック・ループ

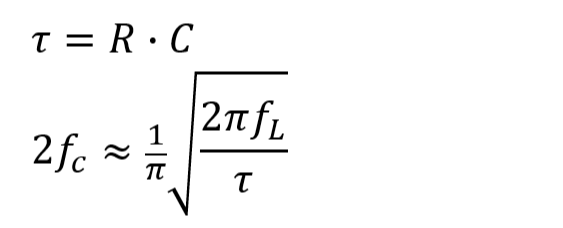

さて、上記からCD4046のデータシートがダウンロードできます。外付けRCフィルタの定数を計算するのに参考にできる式がデータシート中に書かれてました。1か所引用させていただきます。

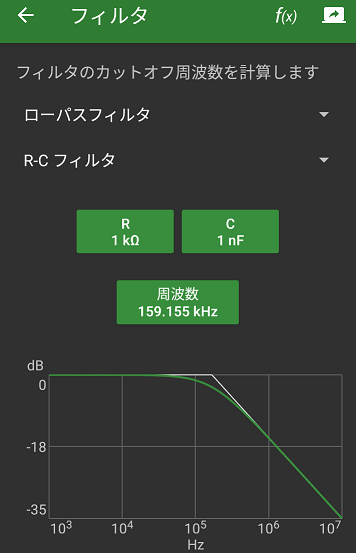

上記の式と前回のVCOの実験から、5V電源のときのfc=420kHzくらい、と見積もりました(いい加減。)そこからこちょこちょ計算して決めたのが以下です。

-

- R=1kΩ

- C=1000pF

一応、フィルタとしての特性は以下のごとし(年寄は自力で計算するのが辛いので、いつもスマホのソフト使ってます。)

fcである400kHz付近は多分大丈夫そうだけれど、低い方はどこまで大丈夫なのか?知らんけど。

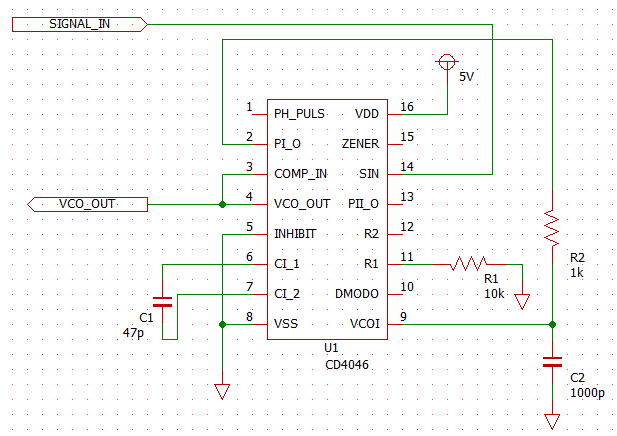

実験に使用した回路

実験に使用した回路が以下に。前回の回路に対して

-

- VCOの出力を位相比較器に直結した

- 位相比較器はIの方(単純なXOR)を利用

- 位相比較器の出力を上記の定数のRCフィルタを通してVCOに入力

CD4046は、もう一つⅡと呼ばれる位相比較器があり、フツーはこちらを使うみたいです。また今度かな。やること多いなPLL。

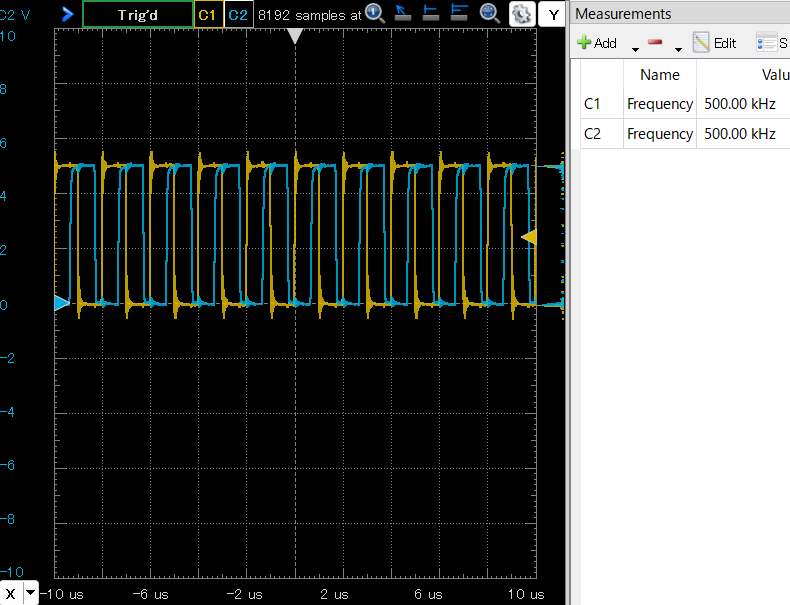

実験結果

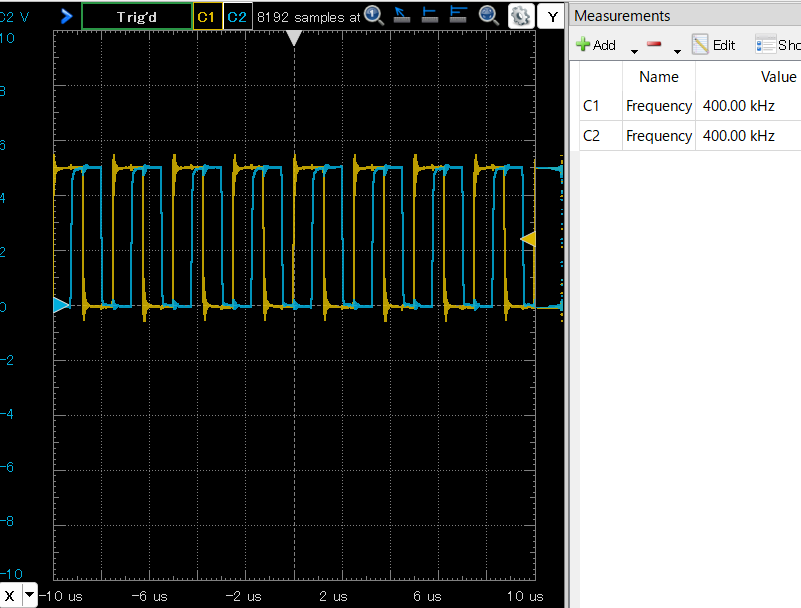

まずは ロックする中心周波数付近になる予定の400kHz付近の波形を見てみます。黄色C1が外部からの入力信号、青色C2がVCOからの出力信号です。気持ちいいくらいピッタンコの周波数が出ております。安定。位相もほぼ90度ズレくらい。予定どおり?

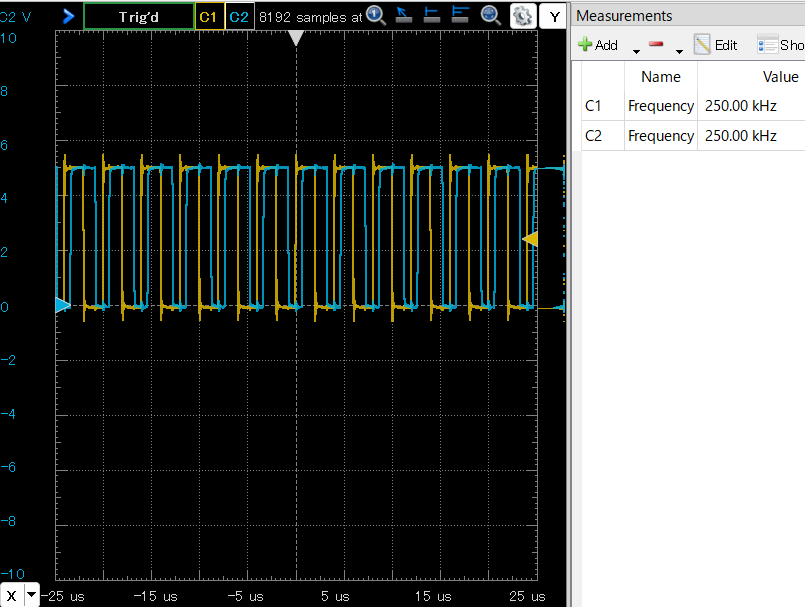

さて、下の周波数、250kHzのときが以下に。ここもロックOKとな。

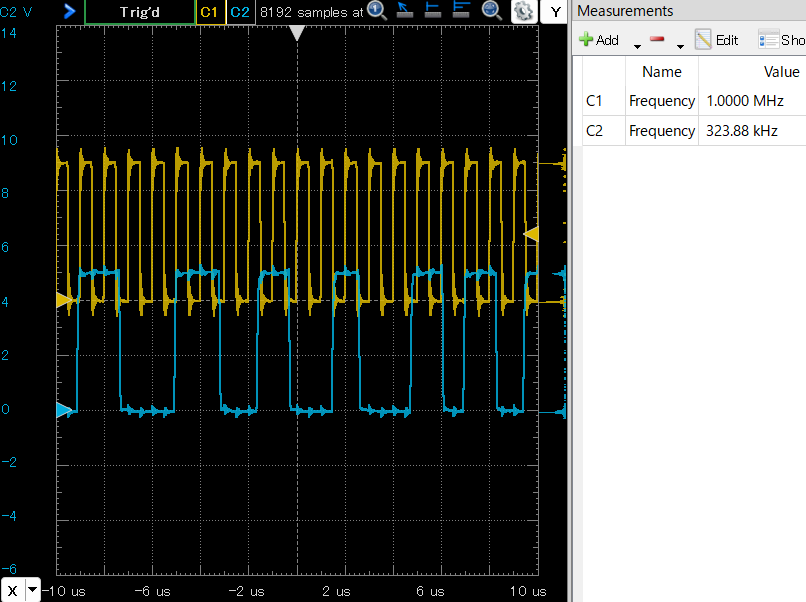

一気に1MHzに上げたら、やっぱりダメでした。ガタガタの波形になってしまって見ずらいので、C1とC2を上下にチョイとずらしてあります。こんな感じ。ロックが外れてしまいましたなあ。

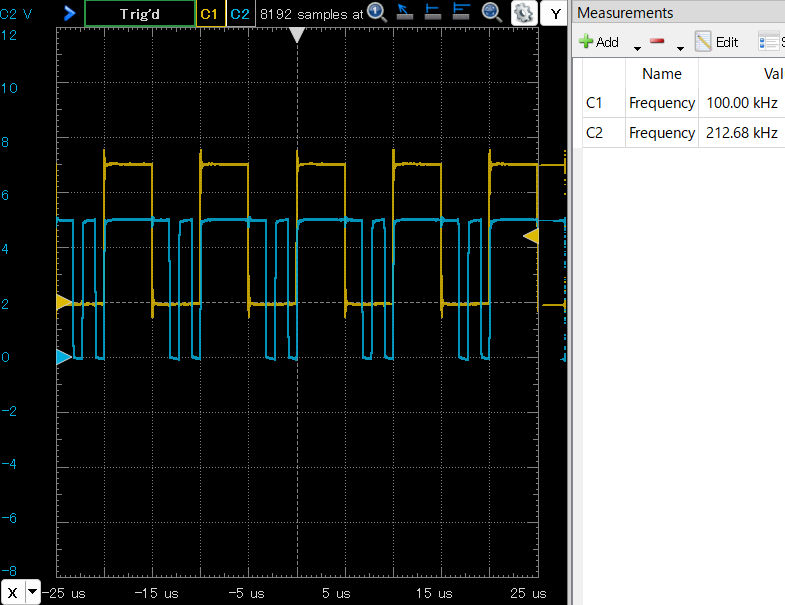

今度は低い方で入力を100kHzまで落としてみました。これまたロックしないね。このアタリの周波数だとLPFがそのまま波形を通してしまう筈なので、VCOには電圧が上がったり下がったりする波形が入力されてしまっているのでしょうな。予想されたことなので致し方なし。

ロック可能な範囲は詳しく確認してませんが、ま、1:1での位相ロックはできるみたいだ、と。次回はN分周回路を入れてN逓倍のクロックを作るぞ、と。