前回までのアナデバM1Kネタを一端終了し、今回からは本題のMOS論理回路話に戻りたいと思います。再開第一回は複合ゲート(コンプレックス・ゲート)と言われるものをCMOSとNMOS(もどき)で作って動作させてみたいと思います。ぶっちゃけ、複合ゲートが作れる程度に例の変換基板の数が溜まってきた、ということなのですが(老眼で辛いので日産2枚?)。

※かえらざるMOS回路 投稿順 INDEX

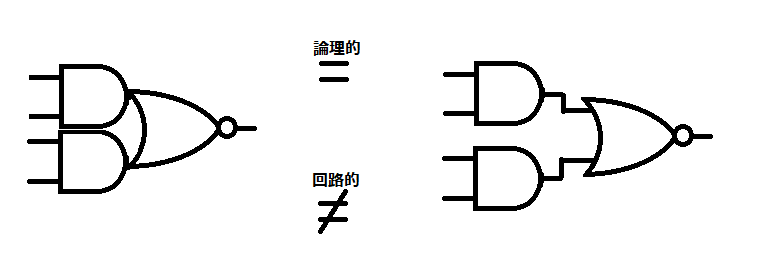

まず、複合ゲート(コンプレックス・ゲート)と言われるものがどのような論理回路であるのか、1例をあげて御覧いただきましょう。

左側が複合ゲート、右側はゲートを組み合わせて「等価」な回路にしたものであります。図でみたらANDゲートのNORの間の線が伸びているかいないかだけの違いです。そして論理的には左右は等価。しかし、回路的には異なります。右の構成をCMOS回路でそのまま作ると16トランジスタ、実際にはANDとNORではなく、NAND3個とインバータ1個で作ると14トランジスタ必要なのですが、左側の複合ゲートであれば8トランジスタで出来てしまいます。

ですから現在のように潤沢にトランジスタを使えなかった昔は結構活用の度合が高かったように思います。別に上のような回路だけでなく、いろいろの組み合わせの複雑な論理ゲートを作れるのですが、一方速度のためにはトランジスタのサイズを調整しないとならない、という性質があります。論理回路といえどトランジスタレベルで設計していた昔はそれでもよかったのですが、設計の自動化が進み、実装方法によってはそんな「カスタマイズ」は排除される傾向にもなり、昔ほど活用されていないように思われます。ま、現在でも利用される局面はある筈なのでCMOS複合ゲートは「帰らざる」の範疇ではありません。

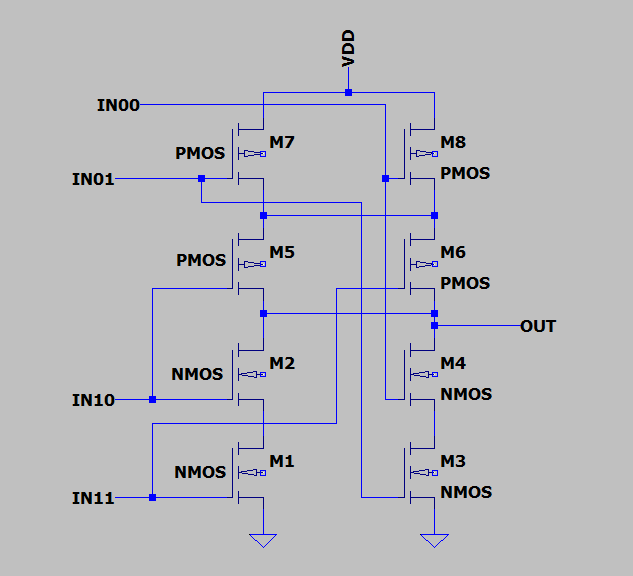

実際に、上の複合ゲートをCMOSのトランジスタレベルで描いた回路図を下に示します。(なお、1点変なところがありますが、その説明は後で書きます)

NMOSトランジスタ4個、PMOSトランジスタ4個で上の論理回路の動作が実現できているのが分かると思います。なお、「変」な部分は、各トランジスタのボディ、サブストレート、バックバイアス、いろいろ呼び方はありますが、矢印が描いてある4端子目をちゃんと接続していないことです。この部分は、今回のようにディクリートのMOSトランジスタとLSIの内部のMOSトランジスタでは異なるために、明示的に描きませんでした。

-

- ディスクリートのMOSトランジスタでは有無を言わさずソースに接続

- LSI内部ではNMOSは接地、PMOSは電源に接続するのが基本

本来MOSトランジスタは4端子素子の筈なのですが、ディスクリートでは3端子扱い。LSI内部では普通のトランジスタは上記のような接続なので、やはり敢えて4端子目を描かないことも多いですが、回路によっては「バックバイアスを振る」みたいなテクを使うケースもあるので4端子目が活躍することもあります。

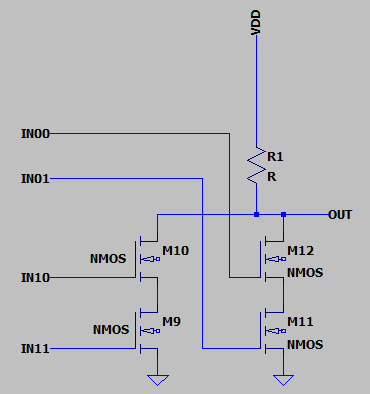

さて、「お待ちかね」の「帰らざる」NMOS回路(もどき)での同じ複合ゲートの回路を御覧いただきましょう。「もどき」なのは、本来デプレッション型NMOSトランジスタで構成されるべきプルアップ抵抗相当の部分が素の抵抗になっているためです。

御覧ください。4トランジスタで先ほどの論理ゲート相当の回路ができてしまいました。CMOS基本ゲートを組み合わせたら14トランジスタ、それをCMOS複合ゲートにすると8トランジスタ、しかしNMOS複合ゲートでは4トランジスタ。トランジスタ数に汲々としていた時代には、この差が大きかったのでした。

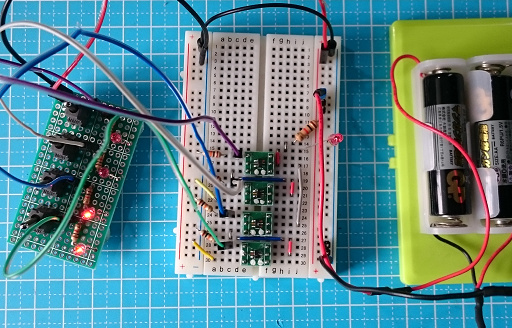

回路図を描いているばかりでは実感に乏しいので、実際にブレッドボード上、ディスクリートトランジスタを組み合わせて上記の回路を組んでみました。

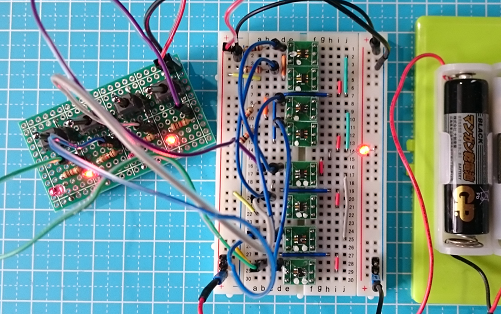

まずCMOS複合ゲートのケース。今回はM1Kを使わず、電源は右側の電池3本で4.5V与えています。入力信号は、左の小さなジグ基板上のスイッチで与えます。それぞれのスイッチでHIGH(1)をあたえるとLEDが点灯するようになっています。そして、中央のブレッドボードがCMOS複合ゲートの回路。中央に8個変換基板が並んでいますが、上の4個がPMOS、下の4個がNMOSです。中央付近で出力信号を取り出しており、ここにもLEDが。点灯でHIGH(1)出力です。結構、配線が醜く飛び回っています。PとNの両方に入力信号を引っ張りまわさないとならないのですね。

一応、LOW(0)が出力できるところもやっておきましょう。回路をみれば分かるとおり、NMOSが直列にならんでいる側の2つのトランジスタの両方に1を入れればLEDが消灯できます。こんな感じ。

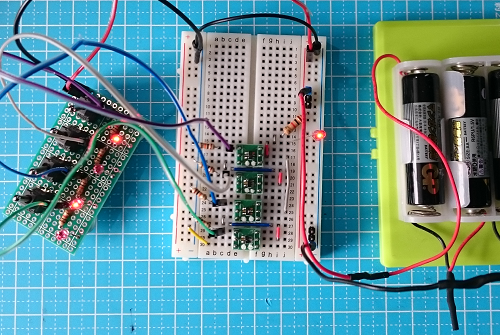

それでは、同じことをNMOS回路でやってみます。NMOS回路版の複合ゲート回路は下です。上のCMOS回路版と比べるとどうでしょうか、

スケスケ

な感じになりました。トランジタの数が半分になっただけでなく、配線もスッキリ。しかし、動作的には上と同様です。まずはHIGH(1)出力。

このように、ディスクリートのMOSトランジスタを使っても、ちゃんと複合論理ゲートが構成できることが分かりました。

この先ね、段々NMOSらしくして行きたいです。でもね、その前にAraha氏からの宿題もやっておかないと。また、M1Kにお願いしますか。