前回はLogisimのライブラリから符号無整数の比較器「組み合わせ回路」をVerilogしてみました。今回はバイナリカウンタ「順序回路」をVerilogしてみます。端から部品を練習すれば、そのうち色々できるだろ~という勝手な思い込みです。記述のお作法もいろいろあるのだけれど、今のところ成り行き。徐々に修正する予定。

※かえらざるMOS回路 投稿順 INDEX

※使用させていただいとります「フリー」ツールのホームページへのリンクは以下です。

Logisim 画面上で論理回路の動作を観察できるツール。左記からダウンロードして実行可能ではあるものの、既に “suspended indefinitely” 状態。

Icarus Verilog 「商用でない」Verilogの定番。

GTKWave Verilog処理系などが出力する VCDフォーマットのファイルをタイミングチャートとしてみるためのビューワー

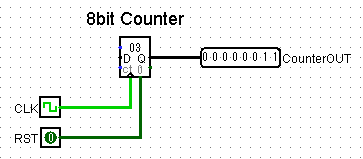

Logisim上のカウンタ

Logisimのライブラリから持ってきたカウンタの最小構成が以下です。とりあえずクロックCLK(ポジティブエッジでクロックアップ)と、リセット信号RST(ハイでカウンタクリア)だけで制御しています。ライブラリ・モジュール的には「カウンタに外部から値をロードするための端子あり」「カウントダウンもあり」なのですが「外部からのロード無、カウントアップ」で使用しています。

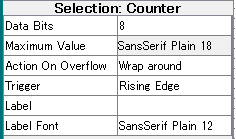

Counterのセッティングが以下に。8ビットです。8ビット範囲を超えたらラップ・アラウンドして0に戻ります。

Verilogで書いてみた

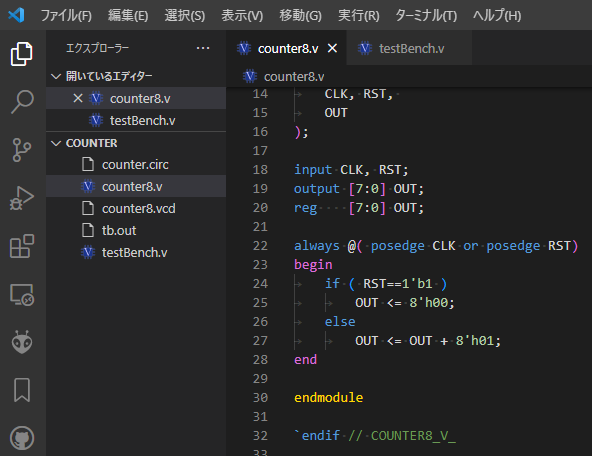

今回は順序回路、RST付きなので、以下のようにしてみました。お作法的にはどうなんだろ~。8ビット・バイナリ・アップカウンタということで。

/** @file

8bit binary counter

*/

`ifndef COUNTER8_V_

`define COUNTER8_V_

/** The COUNTER8 module

@param[in] CLK clock input

@param[in] RST reset input

@param[out] OUT [7:0] counter output

*/

module counter8(

CLK, RST,

OUT

);

input CLK, RST;

output [7:0] OUT;

reg [7:0] OUT;

always @( posedge CLK or posedge RST)

begin

if ( RST==1'b1 )

OUT <= 8'h00;

else

OUT <= OUT + 8'h01;

end

endmodule

`endif // COUNTER8_V_

上記の8ビット・カウンタをエクササイズするためのテストベンチが以下に。これまた成り行き。これまた、お作法的にはどんなもんだろ~。

/** @file

testBench.v, to test counter8.v (8 bit binary counter)

*/

`ifndef TESTBENCH_V_

`define TESTBENCH_V_

`timescale 1 us / 100 ns

/** The counter8 testbench */

module counter8_tb;

reg CLK, RST;

wire [7:0] OUT;

parameter STEP = 10;

counter8 dut(

CLK, RST, OUT

);

initial begin

$dumpfile("counter8.vcd");

$dumpvars(-1, dut);

$monitor("%d OUT=%d", $stime, OUT);

end

// testbench actions

always begin

CLK=0; #(STEP/2);

CLK=1; #(STEP/2);

end

initial begin

#0 RST = 1'b1;

#STEP RST = 1'b0;

#(STEP*260) $finish;

end

endmodule

`endif // TESTBENCH_V_じ

実行してみた

お作法はともあれ、実行してみれば動作はOK、こんな感じであります。

$ iverilog -o tb.out testBench.v counter8.v $ vvp tb.out VCD info: dumpfile counter8.vcd opened for output. 0 OUT= 0 15 OUT= 1 25 OUT= 2 35 OUT= 3 45 OUT= 4 55 OUT= 5 65 OUT= 6 75 OUT= 7 85 OUT= 8 95 OUT= 9 ~途中略~ 2555 OUT=255 2565 OUT= 0 2575 OUT= 1 2585 OUT= 2 2595 OUT= 3 2605 OUT= 4

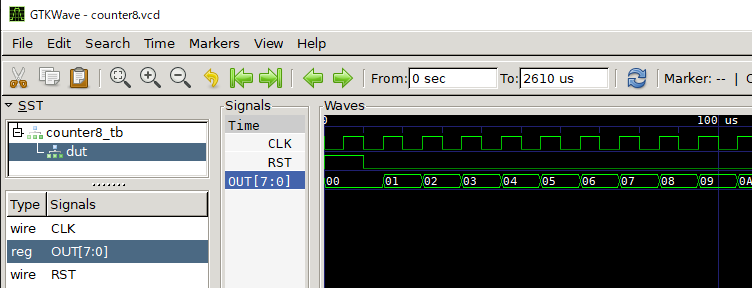

上記の$monitor出力で動いているのは明らかですが、念のためVCDビューワーで波形として観察してみます。

$ gtkwave counter8.vcd GTKWave Analyzer v3.3.100 (w)1999-2019 BSI [0] start time. [2610000] end time.

カウンタしているようです。当たりまえか。