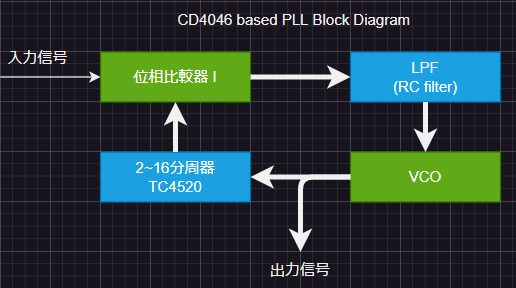

前回、CD4046を使って入力クロックと1:1でフェーズロックする回路を実験しました。でも1:1ではPLLっぽくないすよね。今回は4ビット・カウンタ、TC4520BPを分周器として使用してみます。VCO出力と位相検出器の間に分周器を挿入し、クロックを逓倍してみます。控えめ?な2逓倍ですけれども。

※「定番回路のたしなみ」投稿順Indexはこちら

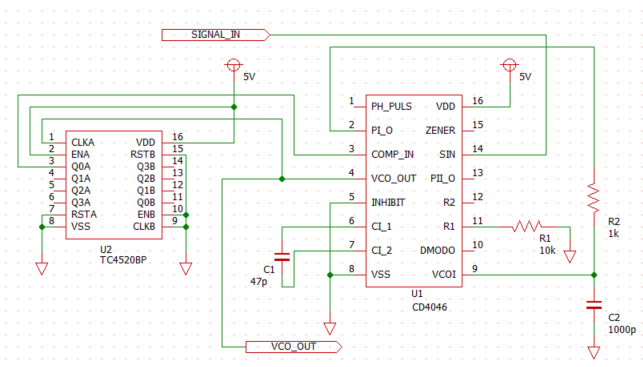

今回実験する構成

TC4520の登場で、ようやく役者がそろい、以下のような構成となりました。ダラダラやっているので3回を要しましたな。

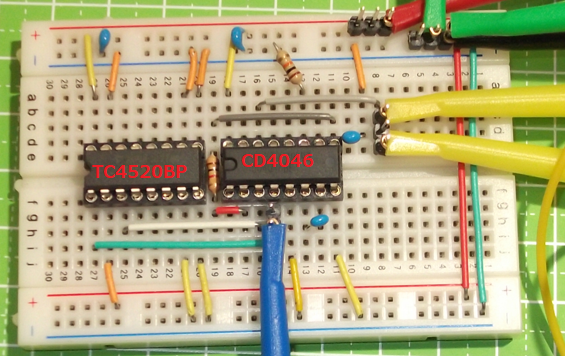

さて、登場したTC4520、なんのことはありません、4ビットのカウンタ回路です。勿論CMOS。1パッケージに4ビットのカウンタが2個入っているので、片方の出力をもう片方のクロック入力に接続すれば8ビットにもなる優れもの?です。

データシートみるとバイナリだけでなくBCDカウントもできるように書いてありますが、BCDカウントするのはどうしたらよいのでしょう?外付け回路いるんでないかい。

今回実験の回路

今回実験の回路では、TC4520のA側のカウンタのみを使います。VCOから出力された出力をA側のクロックに入力し2分周出力から信号を取り出して位相比較器に戻してます。他の部分は前回と同じです。

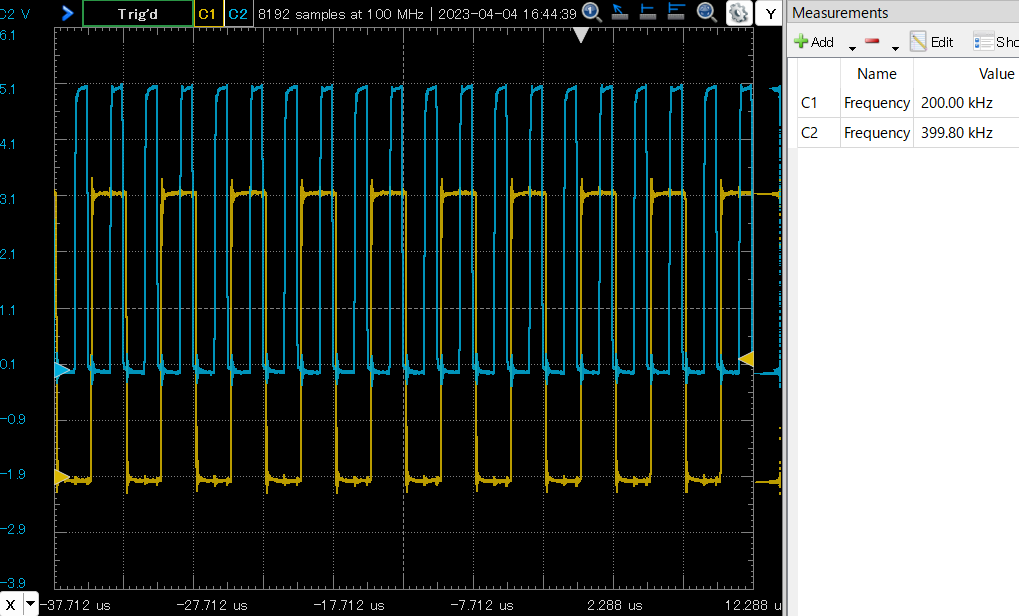

実験結果

ねらい目(VCOの中心周波数)が400kHzちょいということで、まずは入力周波数を200kHzに設定してみました。C1の黄色が入力周波数で、C2水色がVCOの出力波形です。こんな感じ。

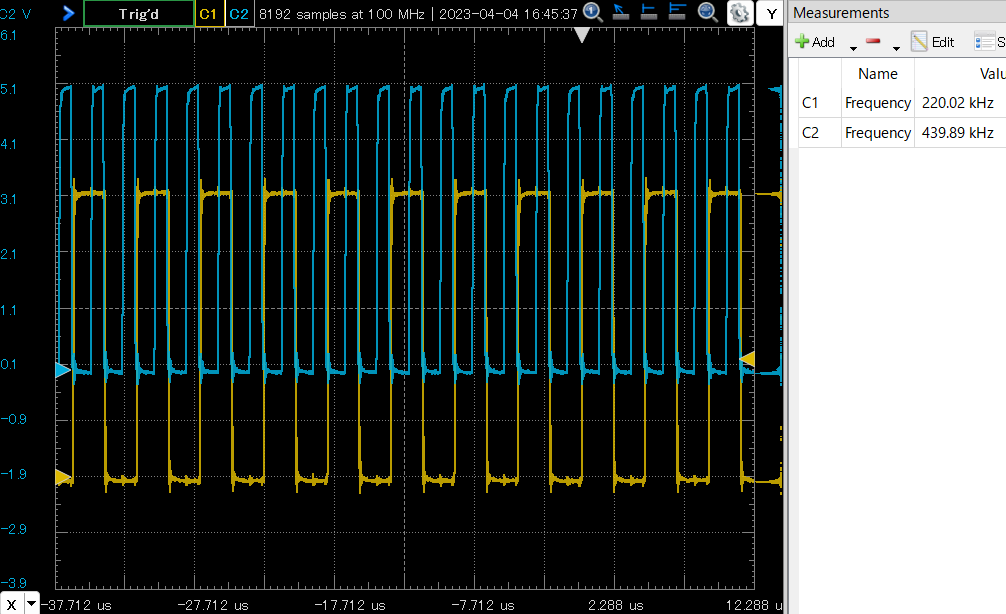

微妙に入力周波数をズラしてみました。220kHzとな。1割アップね。C2はちゃんと追従して440kHz付近でロックしてます。

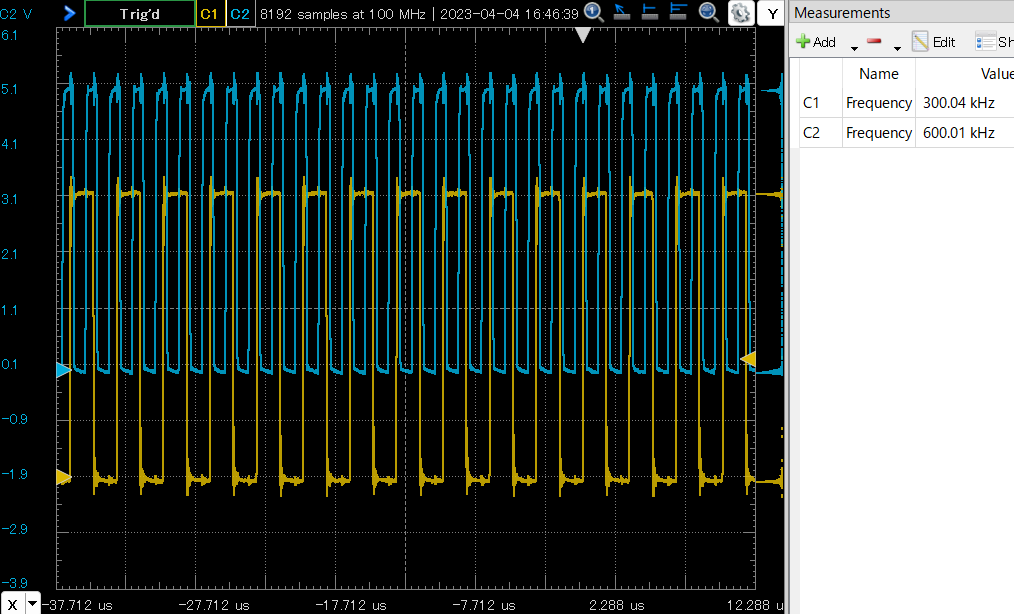

エイヤーということで入力は300kHz。出力は600kHzで依然ロック。

調子にのって入力を400kHzに上げたら、ロックが外れてしまいました。まあVCOの特性を考えれば限界か。

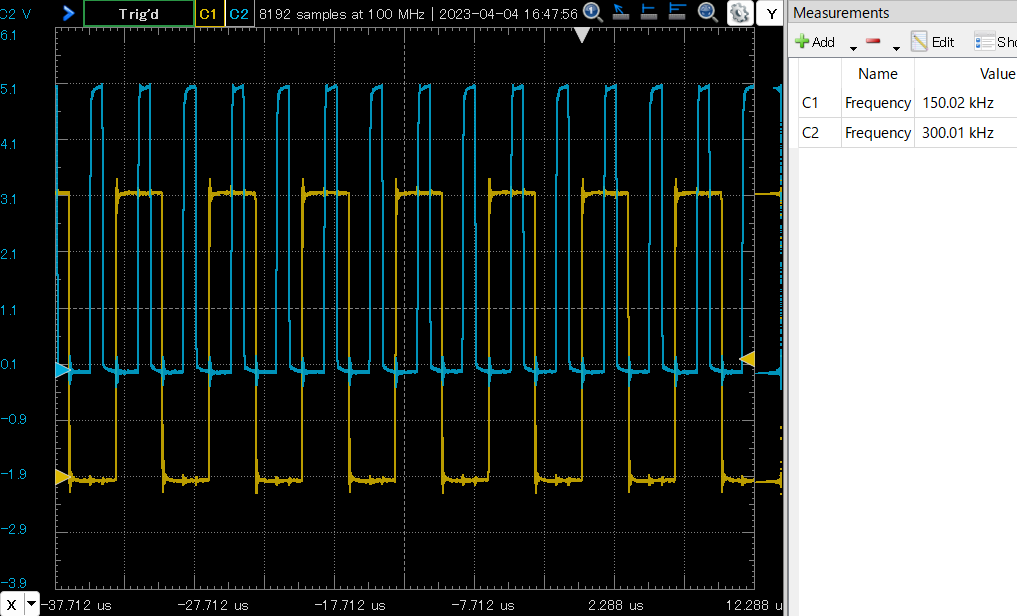

こんどは下の方、入力150kHzでどうよ。出力300kHzでロック。

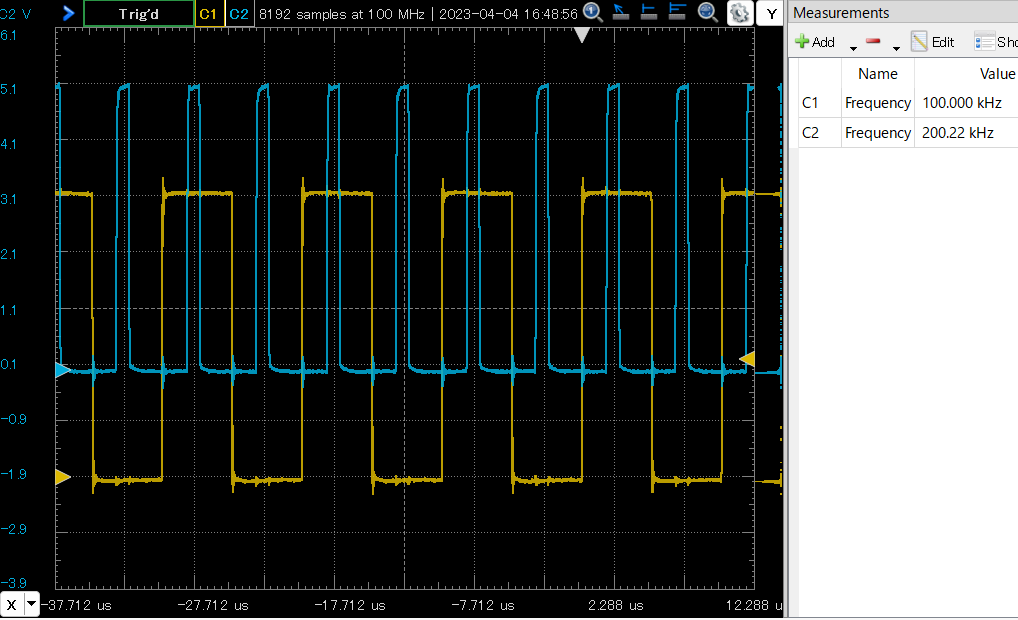

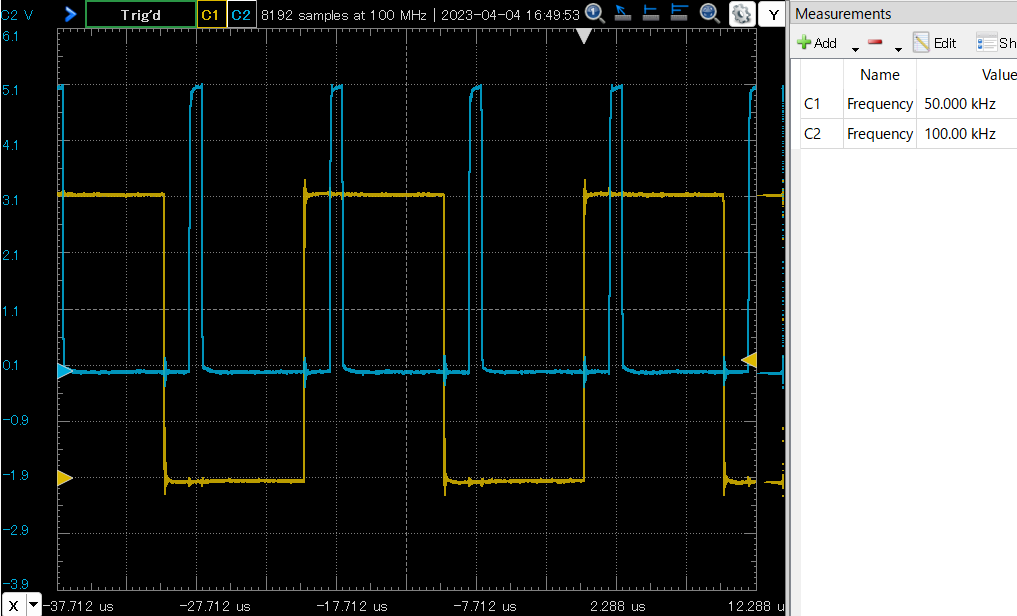

50kHzでどうよ。100kHzが出てきました。そろそろ限界の筈なんだが。意外と粘る?

一応、2逓倍の周波数は作れているみたい。大丈夫か。