FPGAも素人ならVerilogも素人の老人です。適当な題材で回路を作製してシミュレーションしてCMOD S7上で動かしてみることをせねば折角のCMOD S7を使えるようになる気がしません。そんなとき別件シリーズでBCDデコーダ74HC42をいじりました。素人老人にはこのくらいのロジックから始めるのがいいんでないかい?

※かえらざるMOS回路 投稿順 INDEX

※Digilent CMOD S7のマニュアルは以下のページにあります。

なお、CMOD S7搭載のFPGAは「多分、お求めやすい」XC7S25-1CSGA225Cです(Spartan-7シリーズ。)

※実習には AMD社(Xilinx) Vivado 2023.2 を使用させていただいております。

BCDデコーダ

別件シリーズでBCDデコーダをいじった記事は以下です。

お手軽ツールで今更学ぶアナログ(182) AD2のSTATIC IO機能試用、デジタルなのよ

CMOD S7と同じ Digilent社の「アナログ学習用万能簡易ツール」Analog Discovery 2の「いままで使ってなかった」機能を使ってみるの回であります。素人老人がVerilog書いてみるには、BCDデコーダくらいがちょうどいいんでないかと。

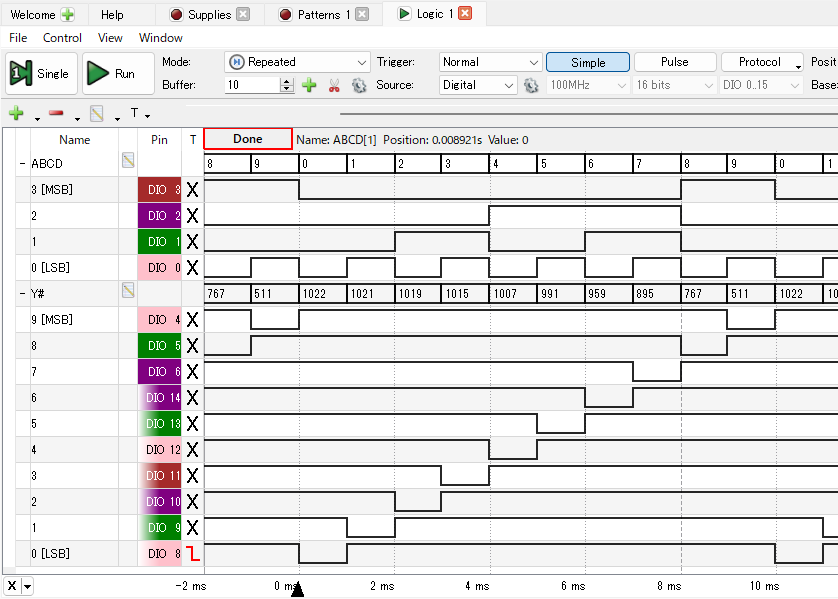

上記別件記事で、現物動作させて波形をとったものを再掲します。

下の方にY#(ローアクティブ)の信号があり、0から9まで1個だけがアクティブになるようになってます。とりあえず、上記と同じ動作を目標に、CMOD S7をターゲット機にVerilogソースを作製、Xilinx(AMD) VivavoのVerilogシミュレータで動作を確認すべしと。

Verilogプロジェクト

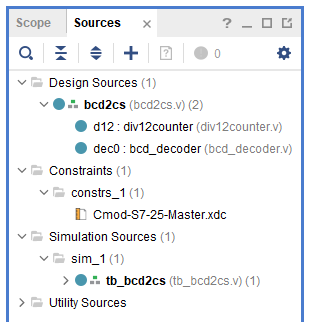

すでに過去回(第44回)でVivadoのVerilogシミュレータは動かしてみてますが、たった1ゲートでした。手順はそのときと同じですが、多少は内容増えてます。まず、プロジェクトの構成は以下のようです。

Design Sourcesの下にVerilogソースが3つ。こいつらが後でFPGA上に実装される回路部分。

-

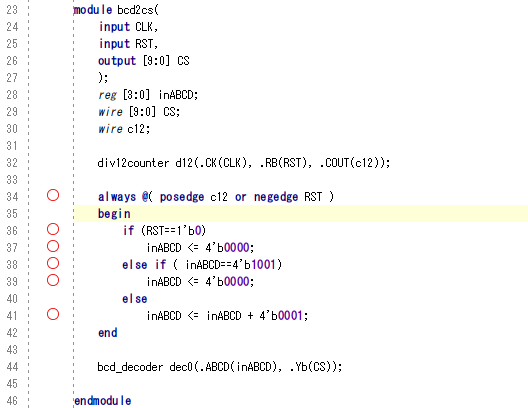

- bcd2cs、回路のトップ、BCDカウンタに入力データを与えて、チップセレクト信号的なものを出力させるトップモジュール。入力データは下のモジュールのクロック出力で10進カウンタを駆動して生成。

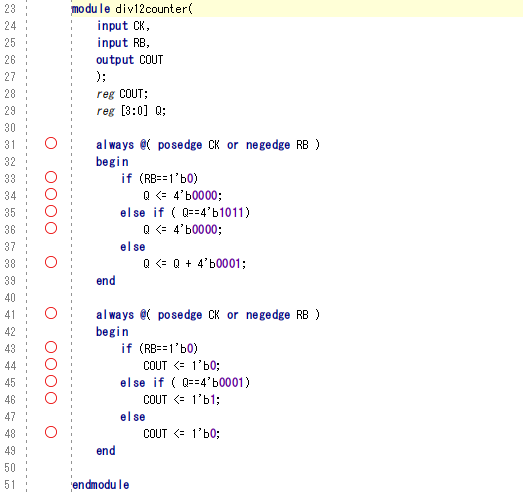

- div12counter、CMOD S7ボード上の12MHzクロックを12分周して1MHz(デューティ112分の1だけれども)クロックを生成するモジュール。

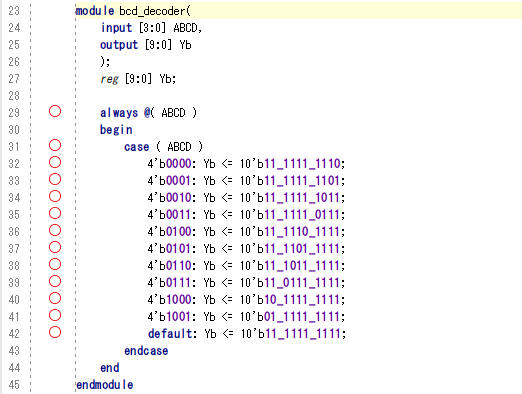

- bcd_decoder、74HC42とほぼ同等のBCDデコーダ本体。74HC42は非同期だけれども、こちらはクロック同期式っす。

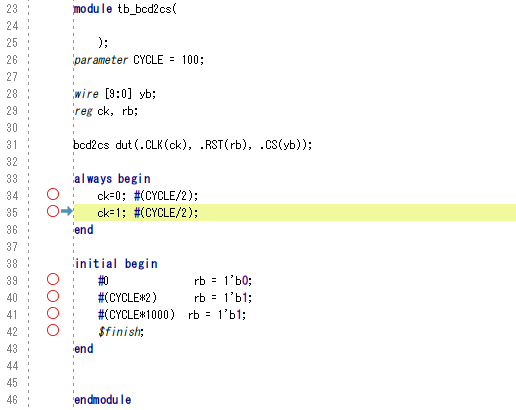

これにとりあえずのシミュレーション用のテストベンチとして tb_bcd2csを加えました。

-

- bcd2cs、トップ・モジュール

-

- div12counter

-

- bcd_decoder

-

- tb_bcd2cs

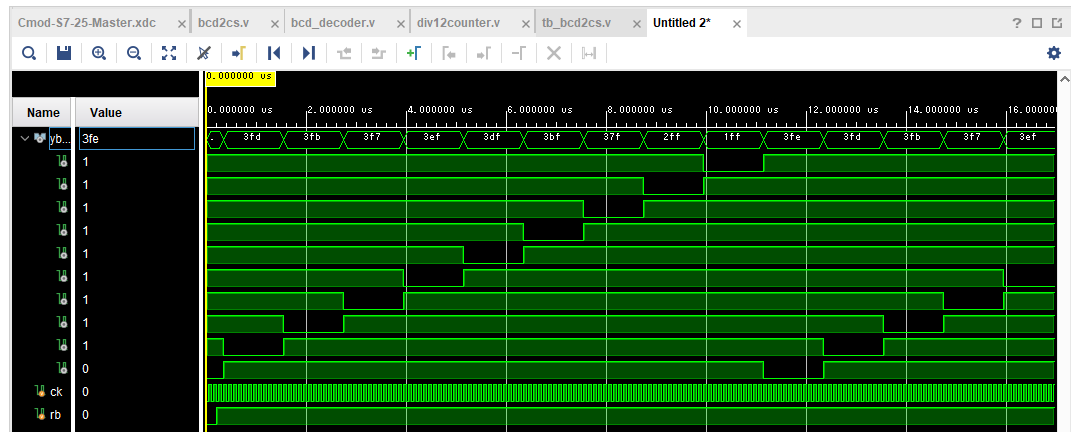

シミュレーション結果

まあ別件の実機を動かした波形とほぼほぼ同じってことでいいか?

このくらいなら、実装まで一気にやれよ、自分。今週はお疲れ。