前回Digilent社の小型FPGAボードCMOD S7を導入。「本流FPGA」Xilinx(AMD)登載であります。開発環境はVivadoのML版です。前回はボードを取り出して「とりあえず」LEDを点滅させる回路をFPGAに書き込み動作を確認。今回はVivadoのVerilogシミュレータを使用してみます。

※かえらざるMOS回路 投稿順 INDEX

シミュレータの使用

Xilinx(AMD)の開発環境 Vivado にはFPGAの回路を合成するためのツールだけでなく、設計検証のためのシミュレータも搭載されています。今回はそのロジックシミュレータの使い方をDigilent社のチュートリアルページを参照しながら練習してみたいと思います。参照するページは以下です。

-

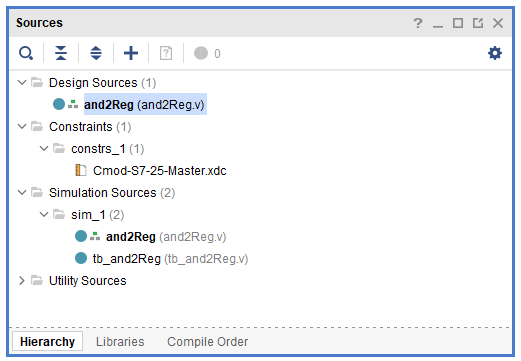

- 「ハードウエアのみプロジェクト」を作製する。その際、Project Nameを設定後、Project TypeはRTLとしておく。また、その時点で 制約ファイルは未設定、ボード選択はDigilent社CMOD S7を選択する。

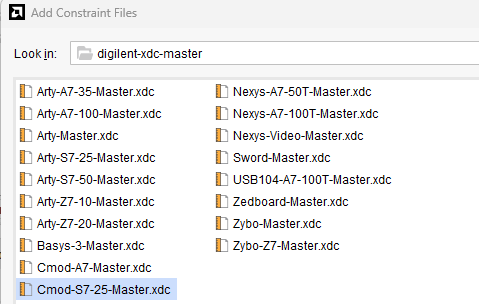

- 前回、Digilent社のウエブサイトからダウンロード済の制約ファイル群の中からCMOD S7用の制約ファイルをCOPYオプションでプロジェクトに加える。

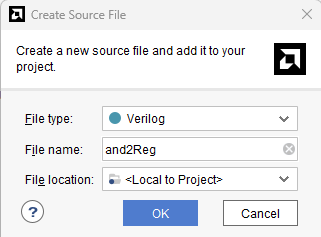

- ターゲットのRTLソースを新規作成する(Verilog, ローカル。)

- ターゲットのRTLソース(実際にはほとんどゲートレベル回路だけれども)を記述。上記例では3入力AND+レジスタだったが、当方では2入力AND+レジスタに手抜き。

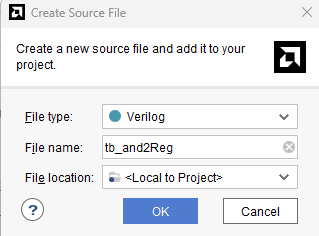

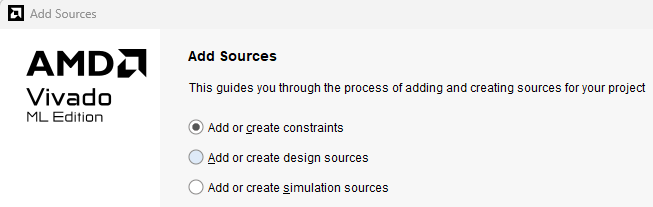

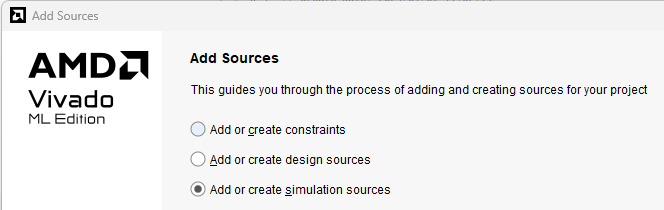

- Add Sourcesでシミュレーションソース(テスト・ベンチ)を追加。この際、上記のチュートリアルでは、SystemVerilogで記述しているが、フツーのVerilogで記述。

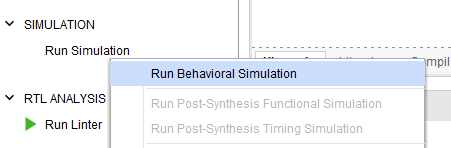

- Run Simulationでシミュレーション、波形ビューワーが起動され、シミュレション波形が予定通りだったらOKとする。

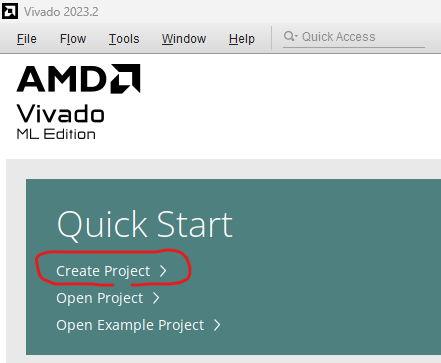

Vivadoの起動から

Vivado起動後の画面の左上隅あたりの様子が以下に。Quick StartからCreate Projectいたしますぞ。

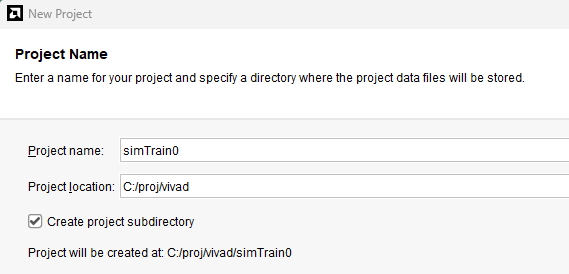

プロジェクト名とファイルなどを保存するロケーションを聞かれるのでテキトーに答えておきます。

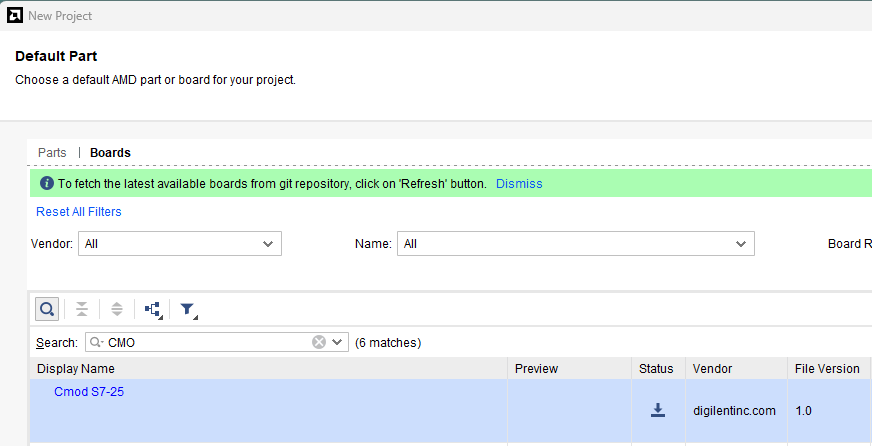

他にもいろいろ聞かれますが、重要なのはDefault Partというところで、Parts(個別のデバイス)ではなくBoardsを選択し、前回一覧表示されるよう設定済のDigilent社のボードの中から Cmod S7-25を見つけることです。ただしステータスは「ダウンロードしてね」印になっているので、ダウンロードボタンを押してダウンロードいたします。

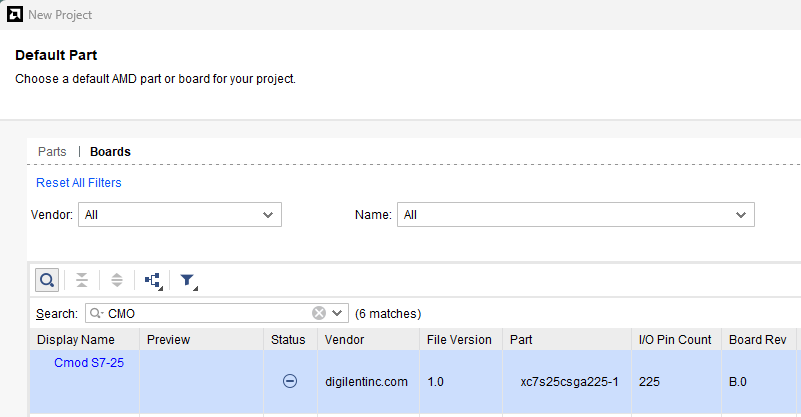

するとパーツナンバやらピン数などが表示され、ボードのあれこれの情報がセットされます。次へ。

ソース(ターゲットの回路の)設定は、Verilogでローカルとしておきます。

また、今回はボード上のFPGAに書き込むわけではないのですが、一応、制約ファイル(constraints)を設定しておきます。Add sourcesからね。

前回ダウンロードした制約ファイル群のフォルダを開き、CMOD S7用のファイルを選択します。その際、勝手に変更しても元ファイルに影響でないようにCOPYオプションにチェックしておきます。

最後にシミュレーション用のソース(FPGAには書き込まれないシミュレーション時のみの部分)のファイルを作製します。

さてソースを記述

ターゲット回路の記述が以下に。Digilent社のチュートリアルでは3入力ANDの先にレジスタでしたが、当方では2入力に手抜きデス。

module and2Reg(

input clk,

input A,

input B,

output Qout

);

reg Qout;

wire D;

assign D = A & B;

always @(posedge clk)

Qout <= D;

endmodule

一方、上記をテストするためのテストベンチの記述が以下に。いいのかこんな感じで。

module tb_and2Reg(

);

parameter CYCLE = 100;

wire qout;

reg a, b, ck;

and2Reg dut(.A(a), .B(b), .clk(ck), .Qout(qout));

always begin

ck=0; #(CYCLE/2);

ck=1; #(CYCLE/2);

end

initial begin

#0 a= 1'b0; b = 1'b0;

#CYCLE a= 1'b1; b = 1'b0;

#CYCLE a= 1'b1; b = 1'b1;

#CYCLE a= 1'b1; b = 1'b1;

$finish;

end

endmodule

シミュレーションをGo

Run Simulationからビヘイビアなシミュレーションを実施するのはこんな感じで。

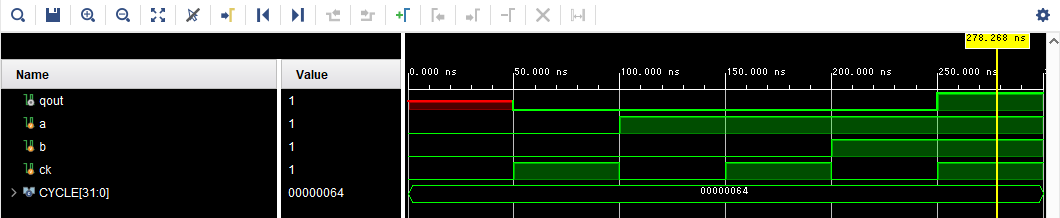

実行後、波形ビューワーのタブが現れてます。a=1、b=1のとき、qoutも1ね。

まあ動いた。2入力ANDとFF1個だけれども。