AlteraはIntelから分離して、再び独立会社になったみたいだけれどもXilinxはどうなんだろ~。知らんけど。さて、前回はBCDデコーダをシミュレーションしたところで「気力が尽きて」しまいました。今回は、VerilogソースをFPGAに実装して動作確認をしたいと思います。シミュレーションと同じ結果になるよね。。。

※かえらざるMOS回路 投稿順 INDEX

※Digilent CMOD S7ボードのマニュアルは以下のページにあります。

なお、CMOD S7に搭載されているFPGAは「多分、お求めやすい」XC7S25-1CSGA225Cです(Spartan-7シリーズ。)

※実習には AMD社(Xilinx) Vivado 2023.2 を使用させていただいております。

制約ファイルに手を入れてなかった、お間抜け。

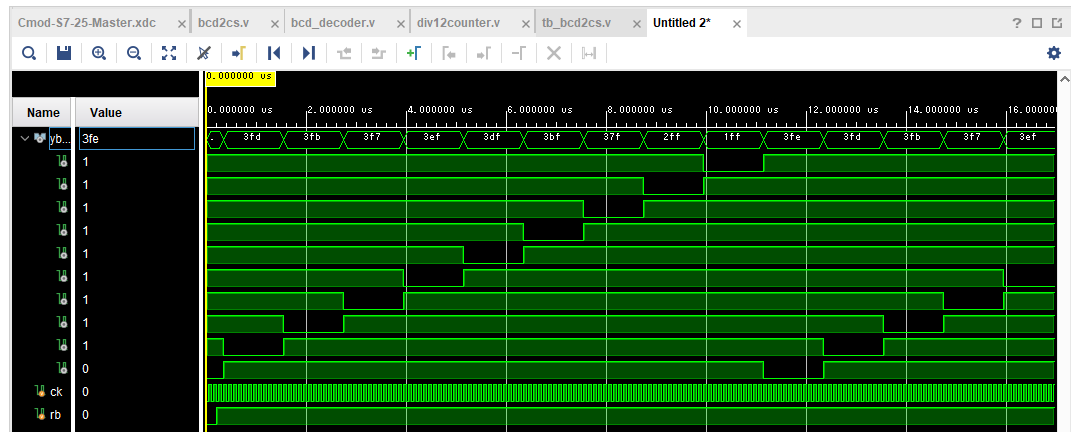

前回、Verilogシミュレーションが無事動作していたみたいなので、今回は何も見ずにシンセシスに突入しました。しかし見事に跳ね返されました。こんな感じ。

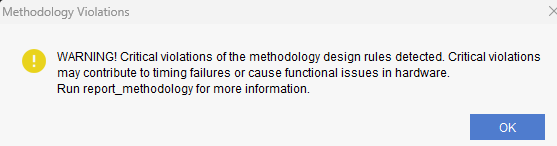

“Critial violations of the methodology” とな。「メソドロジーはCAD屋さんの好きな言葉です。」そういわれると返す言葉もありません。しかし、このポップアップ・ウインドウで目が覚めました。

そういえば制約ファイル、編集してなかったような

CMOD S7ボード用にDigilent社が準備してくれている「標準の」制約ファイルをプロジェクトにコピーした記憶はあるのですが、編集した記憶がありません。「成り行き」で「テキトー」な信号名でVerilogソースを書いていた朧げな記憶。であれば、制約ファイルとVerilogソースの間に何の関係も見いだせないっと。

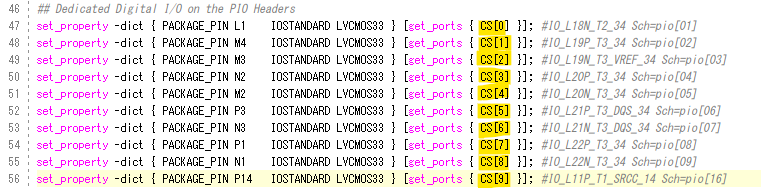

Verilogソースに合わせて制約ファイルを編集

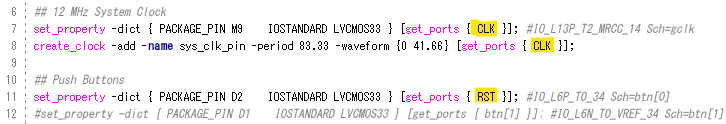

前回作成のソースでは、実体回路のトップには以下3種の入出力信号を書いてありました。

-

- CLK、オンボードの12MHz信号源に接続

- RST、オンボードのBTN0に接続

- CS[0]からCS[9]、DIP式端子のpio0からpio9、pio16に接続

制約ファイルを編集して、信号名と接続されるべき実体を紐づけないとFPGAに実装できる筈がありません。まずはCLKとRST信号。黄色のマーカ部分が編集したところ。

シンセシス、インプリ、ビットストリーム作って書き込み

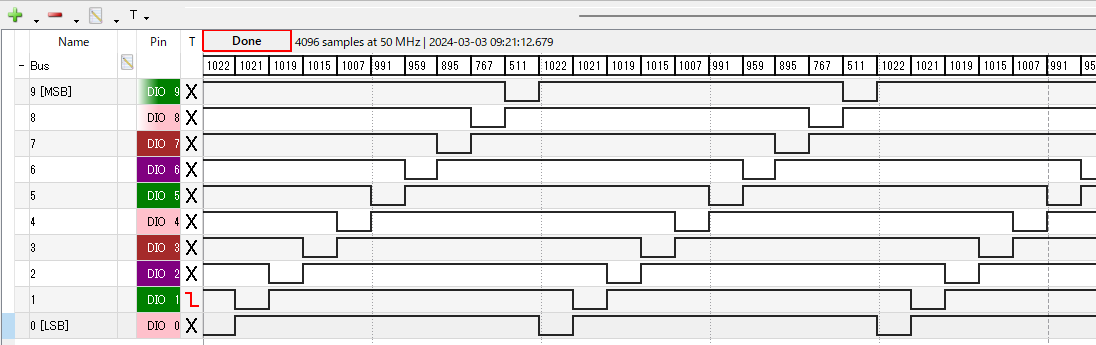

上記を直したら、ポップアップ・ウインドウも消え、ビットストリーム生成まで通りました。CMOD S7ボードをホスト接続し、ビットストリームを書き込み。動作結果は出力にアサインした端子どもにDigilent社Analog Discovery2のロジアナ端子をとりつけて、ほぼほぼシミュレーションと同様な波形を取得しようという目論見です。

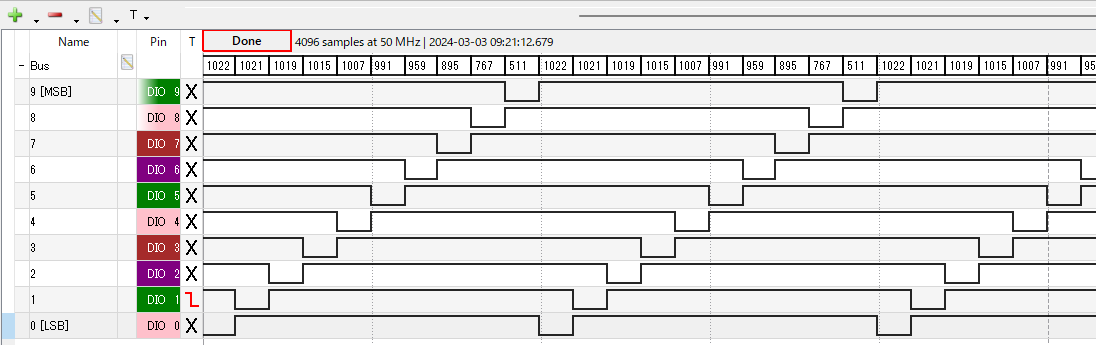

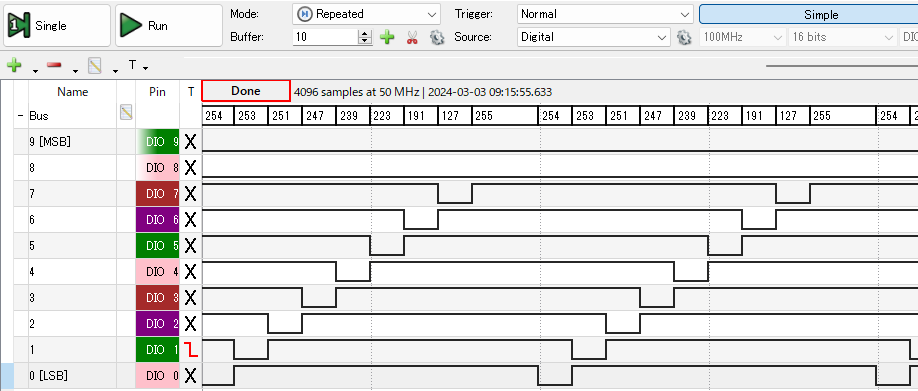

下の方の8ビットはなんか動いているけれど、CSのビット8とビット9が動いてないみたいじゃん。いつものお間抜けね。ロジアナ端子は8本分ずつまとめてあるのですが、8本しか接続してなかったデス。もう一方の8本から2本借りてきて追加したところが以下に。

動いている感じ?

ダイジョブそう? いい加減だな。自分。