前回はモジュールをパラメータ化して再利用しやすくしてみました。今回は、シミュレーション結果をテキストファイルに落として機械的な照合や回帰テストをしやすくしたいと思います。作成した回路を最初観察するときは波形ビューワー使っても、シミュレーションは何度も行うものなので結果確認は自動化しておかないと後が大変。

※かえらざるMOS回路 投稿順 INDEX

※フリーのVerilogの定番、Icarus Verilogの以下のバージョンで動作確認を行っております。

Icarus Verilog version 11.0 (devel) ()

ホームページが以下に。

今回の被テストモジュール

今回は信号線のどこかに1が立っていたらそれをエンコードする回路を被テストモジュールとして使いたいと思います。ぶっちゃけ『お手軽ツールで今更学ぶアナログ第110回』で「フラッシュ型」ADコンバータの出力をエンコードするのに使っている回路をちょいとグレードアップ?したもの。

/** @file

4to2 encoder

*/

`ifndef ENC4TO2_V_

`define ENC4TO2_V_

/** The 4to2 endocer module

@param[in] IN [3:0] signal to be encoded.

@param[out] OUT [1:0] encoded output

*/

module enc4to2(

IN,

OUT

);

input [3:0] IN;

output [1:0] OUT;

reg [1:0] OUT;

always @( IN )

begin

case( IN )

4'b0001: OUT <= 2'b00;

4'b0010: OUT <= 2'b01;

4'b0100: OUT <= 2'b10;

4'b1000: OUT <= 2'b11;

default: OUT <= 2'bxx;

endcase

end

endmodule

`endif // ENC4TO2_V_

Verilogのファイル出力

さて今回の本題はテストベンチ側にあります。前回と似た(コピペで持ってきているので似ているのは当然かと)テストベンチのファイルですが、あちこち細かいところに「手を入れて」おります。

今回の目玉は末尾付近の initial 文のところです。被テスト回路(DUT)の入力と出力を「しかるべき」タイミングでファイルへダンプする部分です。なお「いつもの」、$monitorシステムタスクによる画面出力と波形ビューワー用のVCDファイルへの出力は以前と同様です。

/** @file

enc4to2 Test bench

*/

`timescale 1 ns / 100 ps

module encoder_tb;

parameter CYCLE = 100;

parameter HALF_CYCLE = 50;

parameter DELAY1 = 10;

parameter DELAY2 = 90;

parameter MAXCYC = 6;

wire [1:0] BOUT;

reg CLK;

reg [3:0] BIN;

integer i;

integer fd;

enc4to2 dut(

.IN(BIN), .OUT(BOUT)

);

initial begin

$dumpfile("encoder_tb.vcd");

$dumpvars(-1, dut);

$monitor("%d IN=%b, OUT=%b", $stime, BIN, BOUT);

end

always begin

CLK = 1'b1;

#HALF_CYCLE CLK = 1'b0;

#HALF_CYCLE;

end

// testbench actions

initial begin

#DELAY1 BIN = 4'b0001;

#CYCLE BIN = 4'b0010;

#CYCLE BIN = 4'b0100;

#CYCLE BIN = 4'b1000;

#CYCLE BIN = 4'b1001;

#CYCLE

$finish;

end

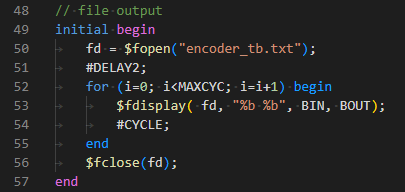

// file output

initial begin

fd = $fopen("encoder_tb.txt");

#DELAY2;

for (i=0; i<MAXCYC; i=i+1) begin

$fdisplay( fd, "%b %b", BIN, BOUT);

#CYCLE;

end

$fclose(fd);

end

endmodule //encoder_tb

実行結果

Icarus verilogのコマンドラインは以下です。

iverilog -o encoder_tb.out -yF:\pgm2\iverilog\vlib encoder_tb.v

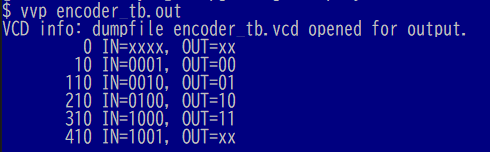

vvpでシミュレーションしたときの画面出力($monitor)結果が以下に。

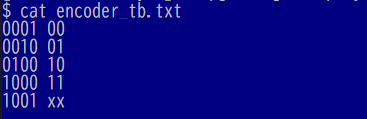

今回追加したテキストファイル出力の内容が以下に。

シミュレーション結果のテキストファイルを貯めておいて、ファイルコンペアかければ、差異があれば分かるので結果確認はらくちんと。

ううむ、すると初回の検証も完全人手ではなくある程度の自動化はしたいところですな。だんだんやること増えてる。。。