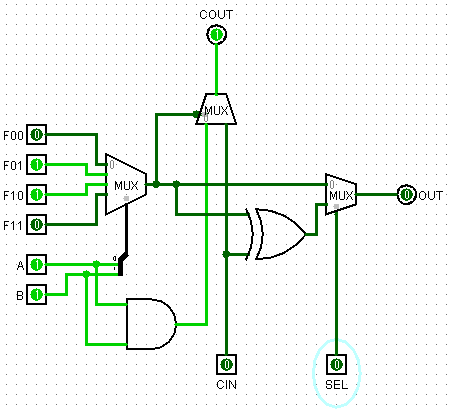

前回はVerilogで無理やりMOSトランジスタ・アレイCD4007をモデリングしてしまいました。MOSFETレベルでも「やれそうな」雰囲気が出てきたので、今回は1bit分のALU(Arithmetic Logic Unit)を試作。分かり易さ優先、正論理のみの「ゲートレベル原理回路」の動作確認をしてみたいと思います。

※かえらざるMOS回路 投稿順 INDEX

※今回はこのところお世話になっております Icarus Verilogはお休み。GUIゲートレベル・シミュレータで原理確認であります。使用させていただいとります「フリー」ツールのホームページへのリンクは以下です。

上記は、画面上でゲートレベルの論理回路の動作を観察できるツールです。入力したその場で「値が見える」ので呆けた頭でもロジック作るのが凄く楽です。上記からダウンロードして実行可能。しかし既に “suspended indefinitely” 状態、残念。

1ビットALU(Arithmetic Logic Unit)

昔は普通にあった?、1ビットALUですが論理合成の発達した今日ではロジック業界の絶滅危惧種かもしれません。2つの1ビット入力(ここではAとBとしています)に対して、設定により所望の論理演算(AND、OR、EOR、NOTなど)と算術演算(加算、インクリメントなど)を実施できる「セル」です。加算ができれば一方の入力を2の補数化することで減算もできるます。なお、今回は掛け算とかシフト系は別なハードにお任せする方針です。

キャリーインとキャリーアウトがあるので、1ビットのセルを積み重ねていけば、任意のビット幅のALUとすることが可能であります。といっても今回の実装は「リップルキャリー」なので高速化テクは何もないです。

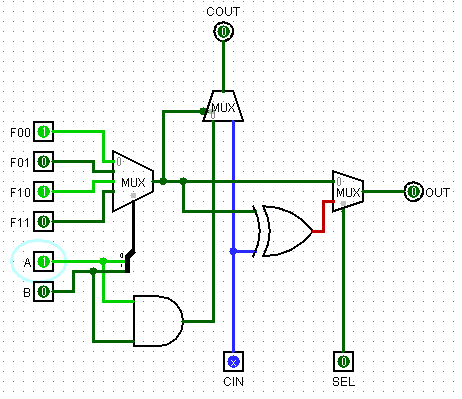

最初、MOSFET(それもNMOS+ウイーク・プルアップ)でNMOS的なALU回路を描こうかと思ったのですが、一端踏みとどまって今回は以下といたしました。

-

- 信号は正論理

- NMOSFETを並べる部分はMUXで代用

NMOSトランジスタレベルで回路をつくるとどうしてもLOWアクティブで負論理になる部分が多い(NMOSはLOWは通せるけれど、HIGHは通しずらい)ので呆けた頭だと間違えそうだったです。「先に正論理で作っておいて」「後からMOSFET」レベルに落とそうとの目論見であります。Verilog化は、このゲートレベルでもOKかな。1ビットのセルが以下に。

入出力は以下のとおりです。

-

- AとB、それぞれ1ビットの値を入力。レジスタAのビットxとレジスタBのビットxに接続する感じ。

- F00、F01、F10、F11、ALUの機能に応じた設定値を入力する。たとえばAとBのANDを取る場合には F00=0, F01=0, F10=0, F11=1 という具合に、AとBの真理値表のとおりの値を設定する。マイコンであればオペコードの中のオペレーションを指定するフィールドをデコードしてここに与えればよい。論理演算はこの部分のみで完結する。算術演算はキャリーを見る必要があるので、ここには、0110(EOR相当)を入力。

- CIN、下位ビットからのキャリー入力。NMOS回路的にはLOWアクティブで行きたいところでありますが、今回は正論理デス。論理演算時には無視。

- COUT、上位ビットへのキャリー出力。

- SEL、ロウのとき論理演算、ハイのとき算術演算の切り替え。

- OUT、1ビットALUの1ビット結果出力。

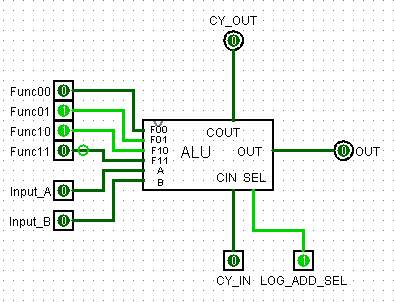

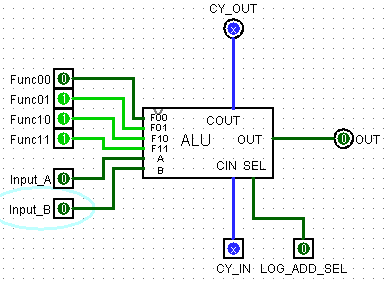

論理演算ANDの時

論理演算なので、LOG_ADD_SELを0にしておきます。ANDの真理値表は、Func00から順に0001なのでこれをFunc端子群に与えます。後はA、Bに適当な値を印加すれば、OUT端子にAとBのANDを取った結果が出力されます。

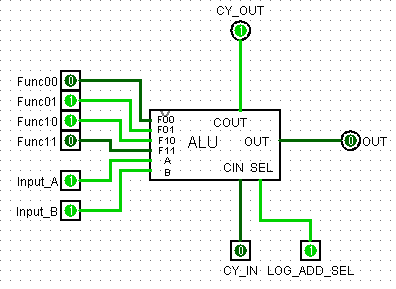

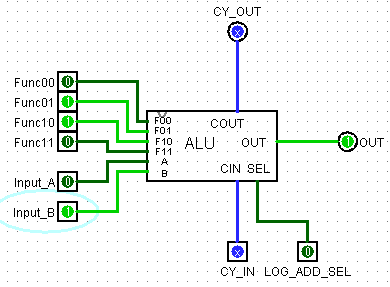

論理演算ORの時

LOG_ADD_SELを0にしておきます。ORの真理値表は、Func00から順に0111なのでこれをFunc端子群に与えます。後はA、Bに適当な値を印加すれば、OUT端子にAとBのORを取った結果が出力されます。

論理演算EOR(Exclusive OR)の時

LOG_ADD_SELを0にしておきます。EORの真理値表は、Func00から順に0110です。以下同文。

論理演算NOTの時

LOG_ADD_SELを0にしておきます。ここでは NOT Aをとることにします。A入力はFuncXYのYの方なので、Yの値の反転をFuncにたてます。1010となります。これでBの値に関わらず、Aの値が出力されます。

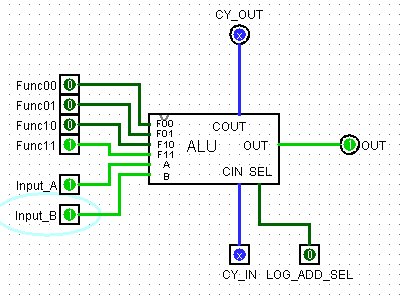

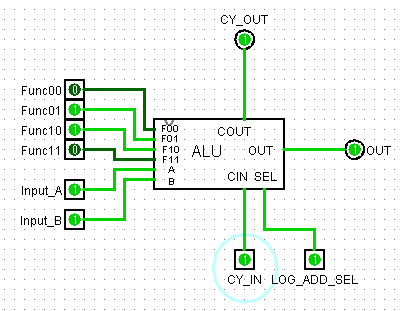

算術演算(加算)の時

LOG_ADD_SELを1に切り替えます。FuncはEOR相当の0110固定です。CY_INでキャリーも制御します。まずはキャリー無0、AB双方の入力が0のケースです。出力は0と。

続いて下の桁からの桁上げ無、AB双方の入力が1のケースです。1+1なので同じ桁の出力は0、上位の桁へのキャリーが1です。

下の桁からの桁上げ有で、AB双方の入力が1のケースです。1+1+下の桁からのCYが1なので同じ桁の出力は1、さらに上位の桁への桁上げも1です。

古式ゆかしい1ビットのALUが出来たので、次回はこのセルを並べて8ビットのALUをVerilog上でシミュレーションしてみますかいな。NMOS回路に落とすのはその後だな、先は長い。