「アナデバ社(ADI社)のWeb記事『StudentZone』を初回からすべて読む」の2022年10月号の実習1回目です。前回に続き今回も論理ゲートです。でもアナデバ様のことです、ロジックで済ませる気は無さそうです。それにその作り方。トランスファゲート使ってます。たまにこういう回路を拝見すると涙がちょちょ切れます。

※「お手軽ツールで今更学ぶアナログ」投稿順 indexはこちら

アナデバ様のStudentZone 2022年10月号記事(日本語版)へのリンクは以下です。

ADALM2000による実習:トランスファ・ゲートを利用したXOR/XNOR回路

前回に続き「万能」のCMOSデバイスCD4007を出発点にして、XOR(イクスクルーシブOR、排他的論理和)/XNOR(イクスクルーシブNOR)回路を作ろう、というのです。CD4007ではトランジスタが足らないのでディスクリートのトランジスタを4個ほど追加してではありますが。

勿論、アナログ回路応用がチラチラしているのでXOR/XNOR作って特性しらべておこうという感じっす。

ただね、そのCMOS、XOR/XNOR回路の作り方が私的にはとても好きなスタイルです。トランスファ・ゲートを使った回路です(アナデバ様は、トランスファ・ゲートと書かれてますが、私個人的にはP、N両チャネル揃ったスイッチはトランスミッション・ゲートと呼びたいです。どーでもいいか。)

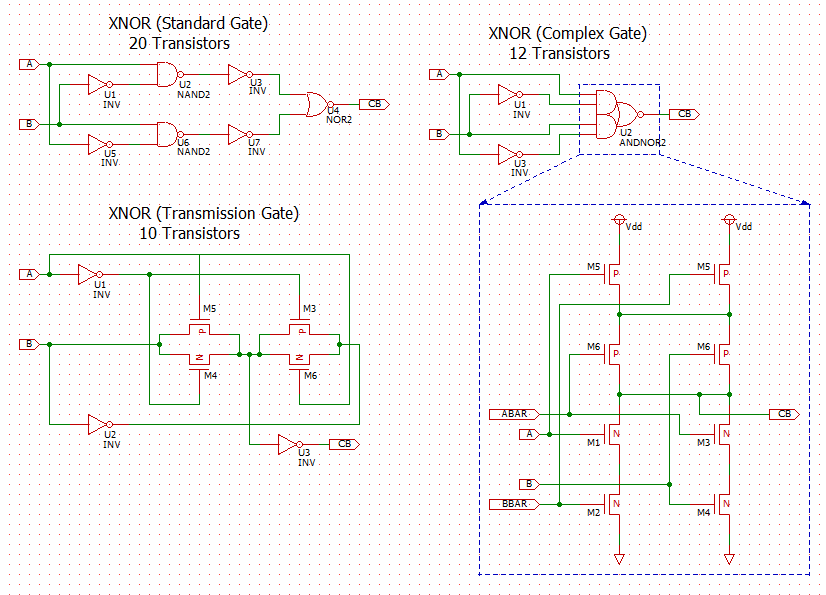

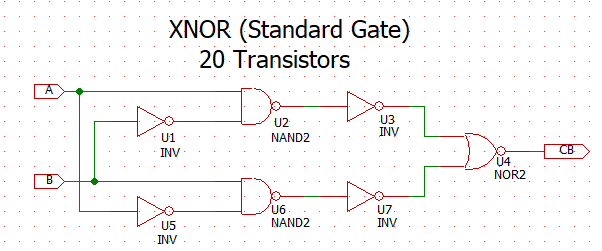

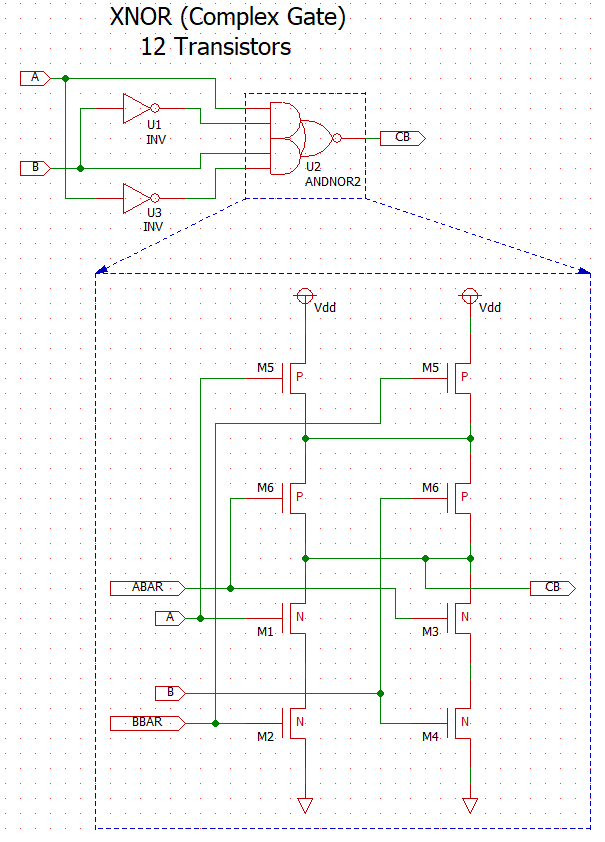

CMOS-IC内でのXNOR回路の作り方その1

P、NのMOSトランジスタからCMOSの論理ゲートを作る場合、論理反転するインバータ、NAND、NORなどは簡単に作ることができますが、AND、OR、単なるバッファなど正の論理ゲートは反転ゲートを組み合わせてつくるのが普通です。使用できるゲートをNAND、NOR、INVに縛った場合、シンプルなゲートでXNOR相当の論理を作ろうとすると以下のようになってしまいます。飛んでもなくメンドイなこれ。

20トランジスタも使っているし、長いパスでは4段もゲートを通過します。遅いっす。

CMOS-IC内でのXNOR回路の作り方その2

アナデバ様は一気にトランスファゲート使った回路にいかれているのですが、勝手に1段階刻ませていただきます。上記のようなXNORの実現はメンドイので、トランジスタレベルでCMOS回路を組み立てるときに使える「コンプレックスゲート(複合ゲート))」を使ってみます。

こんな感じ。20トランジスタが12トランジスタに減った上にパスも短くなりました。

複合ゲートはトランジスタレベルでCMOS回路を設計する場合の定石であります。AND+NOR、OR+NANDの形が基本ですが、端子を増やしたり減らしたり、多段に組み合わせたりと応用が広いです。

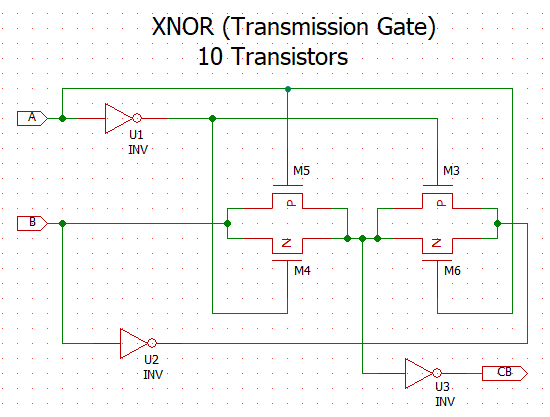

CMOS-IC内でのXNOR回路の作り方その3

そして今回アナデバ様がご指定の回路は、以下の「トランスファゲート」を使った回路です。10トランジスタとな。

この手の遅延の解析がし難い回路はASICの論理設計向きではないかもしれませんが、フルカスタムのCMOS回路であれば、よく出てくるんじゃないかと思います。私は好物っす。

さてアナデバ様の記事は3番目の回路形式をCD4007とディスクリート・トランジスタで構成されているのですが、今回は2番目の複合ゲート構成の動作をLTspcieでおさらいしておこうと思います。

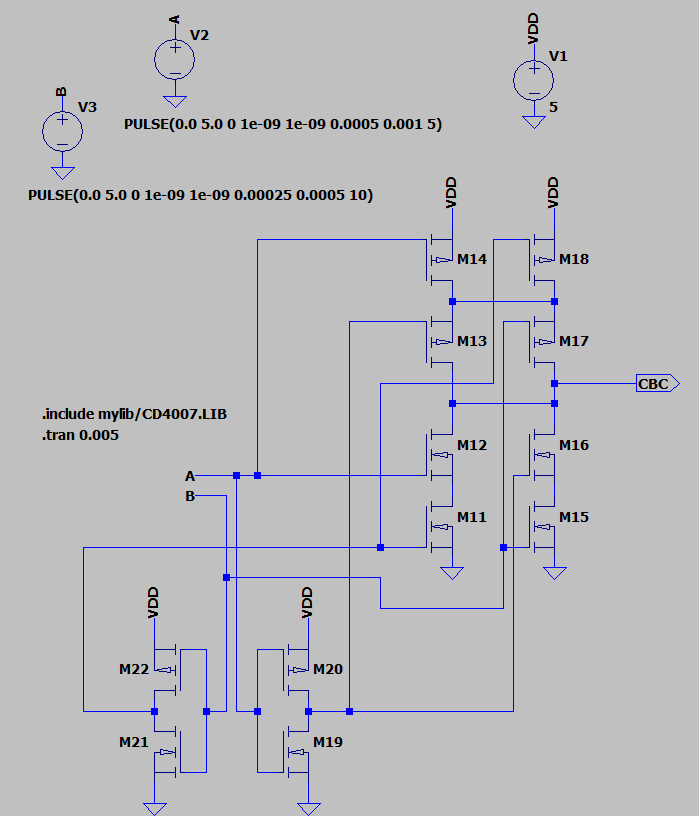

SPICEする回路

LTspiceかけてみる回路は以下のようです。1か所やましいところがあり、この回路のM13、M17、M12、M16の4トランジスタのサブストレート(バックバイアス)の取り方はイカンです。CMOS-ICであればPch、Nchの各トランジスタは同一のウエル内に配置されるのでサブストレートの電圧は共通です。ここでは、3端子のMOSトランジスタモデルを使ってしまったがために真ん中の奴らがちょいとマズイ感じになってます。でもま、多分これでも動くから、コマケー話は気にしないっと。いいのか、そんなことで。

それにMOSトランジスタのSPICEモデル、CD4007用を流用してしまってます。CD4007を2個使ったら正しい複合ゲートが作れる、多分。

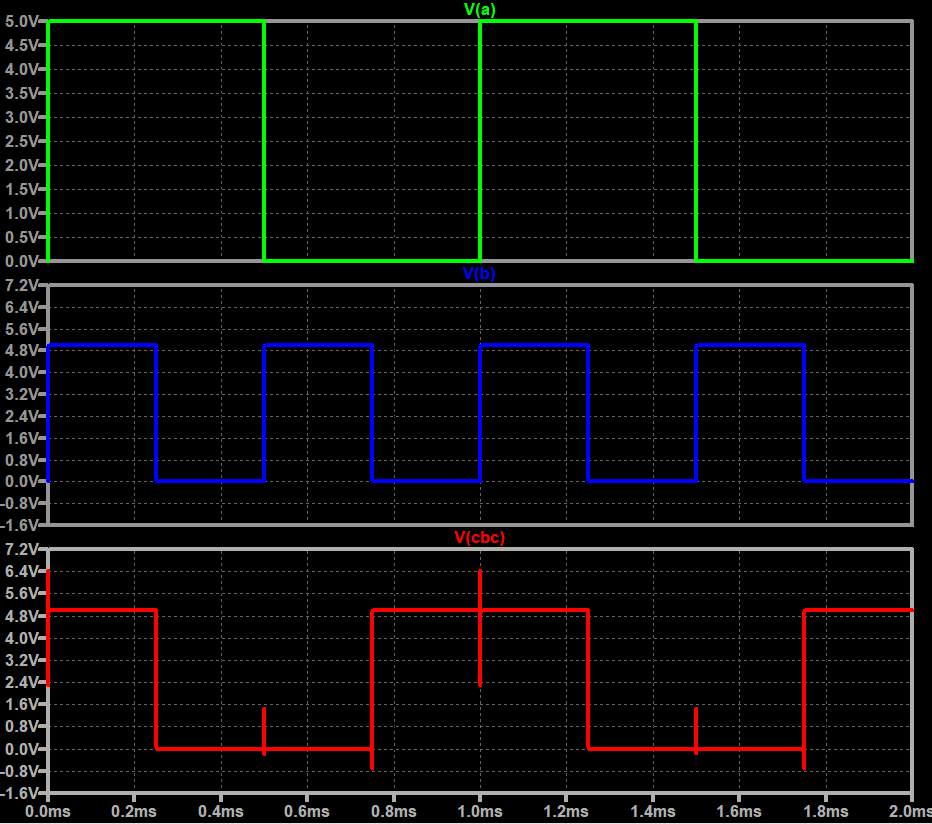

シミュレーションかけた結果が以下に。一番上の黄緑が入力A信号の波形です。2番目の青色が入力B信号です。そして三番目の赤色がXNORの出力信号です。2つの入力が1と0か、0と1の組合わせのときは出力は0(XNORだからXORの反転)、0と0、1と1のときは1だと。

ちゃんと論理動作してますね。来週こそはトランスファゲートバージョンだな。