前回は8085をNOP無限ループに閉じ込めて動かした、という割には一部の制御信号をオシロで当たっただけで「バス動作」らしいところを観察してませんでした。前回の回路では「アドレスバス」が独立してなかったからデス。そこで今回はTTLの代表選手(個人の見解です)74LS373を投入。アドレス・バスを取り出しました。

アドレス・データ・マルチプレクス・バス

インテルの8ビットCPU、8085および16ビットCPU、8086一族(8088含む)はアドレスとデータを1組の信号線上で共用している「マルチプレクス・バス」です。時分割で最初にアドレスを送りだし、後からデータバスに切り替えてデータの読み書きをします。そんなメンドイこと何故したのかといえば、なんとか(無理やり)40ピンDIPに収めたかったからだと思います。当時40ピンDIPまではこなれた「お求めやすい」パッケージだったことに加え、お使いになる方々も楽。それが40ピンを超えてしまうとどちらも結構辛い。当時8086のライバルだったザイログZ8000やモトローラ68000がパッケージのデカさに喘いでいた?(個人の感想です)のに比べると8086はお手軽。

そのかわり「マルチプレクス・バス」は時分割で一つの信号線を共用するので、バスサイクルがかさみます。ぶっちゃけ遅いってことね。その上、今、アドレスがバスに乗っていることを示す信号も必要。この信号が悪名高い?ALE(Address Latch Enable)っす。

ALEの御供、74LS373

今回、おとぼけの8085システム?を作りながらちょっと気になっていたのが、周辺回路を74HCシリーズのCMOSロジックで組んでしまっていることです。8085の時代でもCMOSのロジックICは存在してはいたのだけれど傍流(個人の感想です。)やっぱりロジックICといえば TTL (バイポーラのトランジスタ・トランジスタ・ロジック)が本流。その中でもLS(ローパワー・ショットキ)シリーズが蔓延ってました。よって、8085や8086、8088などのCPUの外側でアドレスとデータを分離したバスにしようとすると登場するのが

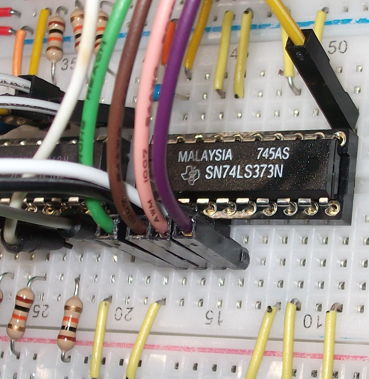

74LS373

でした。CPUが出力するALE信号をこのデバイスに突っ込んでやればマルチプレクス・バス上のアドレスをラッチして保持できるのであります。当時の定石。定番中の定番。

さて今回HCシリーズばかり使っている中で、ココだけはLSシリーズのTTLを使いました。ノスタルジーに浸ったためか、単に「お求めやすい」価格であったためなのか。投げ売り?

御本家テキサス・インスツルメンツ社(TI)殿の製品ページは以下です。

SN74LS373N 3 ステート出力、オクタル D タイプ・トランスペアレント・ラッチ

嬉しいことに「緑のチェックマーク」ありです。この意味するところは「アクティブ」、現流製品であると。風雪幾星霜、74LSシリーズ生き延びてますなあ。

オクタルなので8ビットの8085であれば、これ1個でアドレスバスの下位8ビットをラッチできます。8085の場合上位は独立端子なのでラッチは不要。なお「トランスペアレント」の意味するところは、ALE信号がハイの間、アドレス・データバスに乗っているものがそのまま出ていき、ALE信号がロウになると直前の状態がキープされる(レベルな)ラッチだということです。似た型番で「エッジ・トリガ」なタイプがあるようですがそれとは大違い。

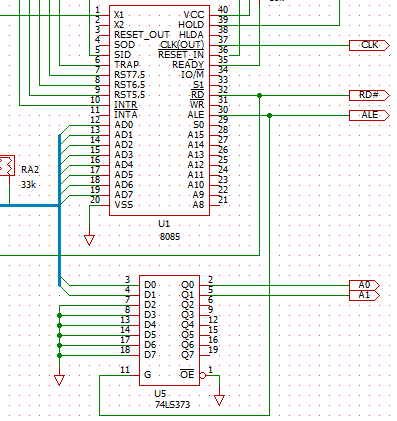

前回回路に74LS373を追加

追加した回路図(差分的な部分)が以下に。今回使用の「手動プログラミングROM」は2バイトしかないので、A0一本あれば事足りるのですが、一応「アドレスバス」として観察したかったので、とりあえず下2本だけ接続しました(本数多いとメンドイから。)

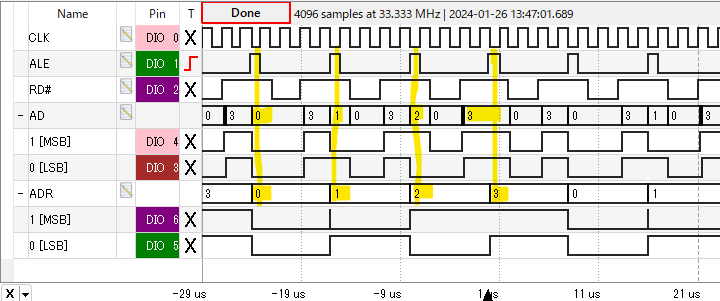

そしてそのときのバスの様子が以下に。

左側のName欄にADと書かれているのがCPUのアドレス・データ・バス端子です(下2ビットしか観察してないけど。)またADRと書かれているのが74LS373でラッチされたアドレス・バスです。

黄色でマーカつけときましたが、ALE信号がハイのときにAD上に出力されている値を拾ってADRにそのまま遠し、ALE信号がローになるとキープするという動作です。ADバスではアドレスを出力するだけでなく、NOP命令(機械語命令コード0x00)を入力しているので、アドレスの途中にゼロが挟みこまれていますが、373のお陰でADRバスには純粋アドレスだけが取り出せていることが分かります。ALEの御供に373。