第12回では「なんちゃってNAND型ROM(もどき)」を作ってみました。ベースになったのは、第11回の直列接続されたNMOSトランジスタ群です。このトランジスタの直列接続はまだまだ噛み応え?があります。今回は、NAND型ROM(もどき)を「改造」してPLA(Programable Logic Array)回路を構成してみたいと思います。

※かえらざるMOS回路 投稿順 INDEX

まず最初に、アイキャッチ画像に掲げた1冊の本をご紹介しておかないとなりますまい。正直に言えば、外出自粛のGW期間中に家の掃除をやったお陰?で見つかったものです。笹尾勤著、「PLAの作り方・使い方」(昭和61年5月10日初版、日刊工業新聞社)であります。昭和61年、1986年。これからバブルへと向かうことになるイケイケの時代が始まろうとしております。今では見るかげもない日本の半導体業界が一時とは言え世界の過半を占めることになる時代の始まりでもあります。MOS論理回路の「古代技術」を振り返っております本シリーズからすると、若干時代は下り、既にNMOSは退役しつつあり、新規設計はCMOSばかりとなって久しい時代であります。

当時、半導体設計の教科書などは多くはなく、また在っても米国人の著書か、その翻訳ばかりだったと記憶しています(今や形見の狭い理工書の中でさらに場末に追いやられていますがそれは別の話。)そんな中、日本人の著者が日本語で書いていた本書は「その界隈」ではエポックメーキングな一冊でした。当時、米国帰りの新進気鋭?の研究者だった著者の力のこもった一冊ではなかったかと推察します(本書出版後、先生のセミナへ行かせていただいたとき、上の本にサインをいだだいとります。)その笹尾先生の「PLAの作り方・使い方」冒頭の1文を引用させていただきます。

AND-OR2段論理回路で任意の論理関数が実現できることは古くから知られており、セルラロジックとして理論的研究が行われていた。

これから説明するPLAという回路は、原理的には全ての「組み合わせ」論理回路」を構成可能な回路であります。さらに、その出力と入力の間にフィードバックとなる経路を設け、そこにフリップ・フロップ(記憶回路)を組み込めば順序回路、有限状態機械(FSM)を構成することも可能。端的に言えば、PLAとレジスタを組み合わせれば、全ての論理回路が作れる(原理的には)、という偉大な回路であります。現在ではFPGAというほとんど全ての論理回路をフィールドで構成可能なデバイスが幅を利かせていますが、その上流へと遡っていくと、比較的小規模なPLDやPALなどのデバイスがあり、それらの源流にはPLAがある、と言えるかと思います。また、本シリーズがターゲットにしているNMOS回路が主流派だった時代には、多くのCPU内部でPLA構造が多用されていました。

「PLAの作り方・使い方」によると、もっとも原始的なPLA相当の製品は、1960年代終わりのHarrisのヒューズ式ダイオードアレイであり、PLAという名称を使った最初の製品は、1970年のTexas Instruments TMS2000JC マスクPLAであったようです。

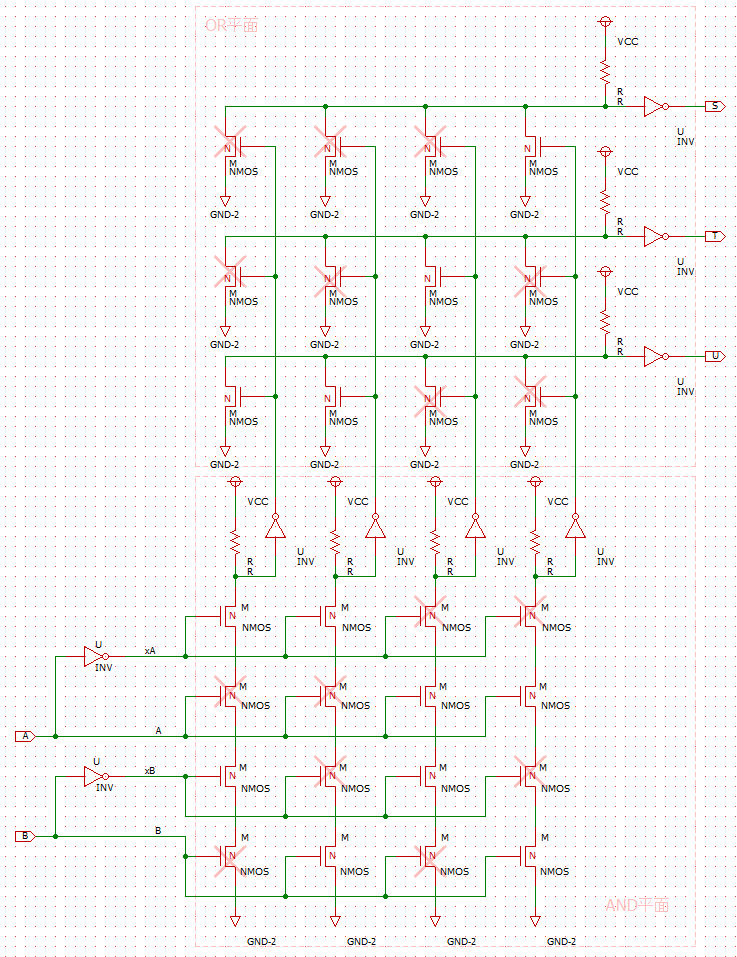

最初のPLA製品である TMS2000JCにして、入力数17, 出力数18、積項数60、フリップ・フロップ10個だったそうですが、今回、なんちゃってPLA(もどき)ということで回路図(例によって水魚堂さんエディタ利用)を下に掲げさせていただく回路は、

入力数2, 出力数3、積項数4、フリップ・フロップ0個

に過ぎません。まあ、規模は極小ですが、原理は分かると思うので勘弁してください。すべてNMOSトランジスタのみで構成されており、大きく下のAND平面と、上のOR平面の2部分に分かれます。下のAND平面はNMOSの直列接続の回路になっており、上のOR平面はNMOSの並列接続の回路になっています。

入力は信号Aと信号Bの二本、出力は信号S,T,Uの3本です。トランジスタの裏側に×印が描いてありますが、これはPLAを「プログラム」した一例を示しています。この回路の場合、AND平面をプログラムする場合は該当(×印)のトランジスタのソース、ドレインをショートさせ、OR平面をプログラムする場合は該当(×印)のトランジスタのドレインをオープンにします。

一応、動作の一例を説明すると、A=0(LOW) B=0(LOW)のとき、一番左の縦方向のラインがアクティブとなります。縦方向を積項(ターム)と申します。すると、OR平面のトランジスタが該当のタームに接続している出力Uは1となり、他のタームがアクティブでなければ出力SとTは0となります。こういう具合に、AND平面で入力値の組み合わせを検出し、OR平面でそのときの出力パターンを記述するという「論理値表」そのものと言える回路が構成できます。

そしてPLAには、ターム数を節約できる良い性質があります。例えば、上の例では、一番左とその次のタームの入力パターンは異なりますが、出力パターンは同じです。つまり、B入力が0でも1でも同じ出力を出せばよいということが分かります。するとBの信号を無視(BとBの反転信号のどちらも×)にしたタームが1つあれば十分ということになります。もっともプリミティブな論理圧縮です。

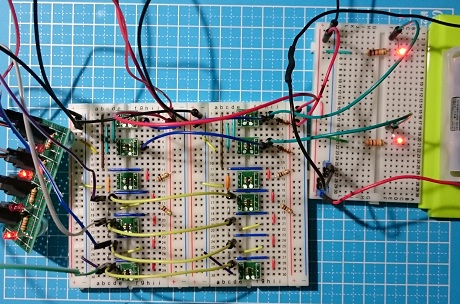

しかしね、実際にディスクリート・NMOSトランジスタBS138を並べて回路を作ろうとしたとき、上記の回路すら大きすぎる、ということに気付きました。手持ち在庫のSOT23表面実装部品をブレッドボードに刺さるようにするBOB基板の全てにBS138を半田づけした(といっても追加は4個)のですが、とても足りません。仕方なく

入力数2、出力数2、積項数2

とさらに回路規模を縮小した上に、

-

- 入力のインバータ省略、テスト用入力4本の隣同士を手動で逆相に設定

- 出力のインバータ省略、信号1が出るときに点灯するLED回路で代用

- トランジスタを×にするところには、トランジスタを置かないで配線で代用

一番左のナナメっている緑の基板が4出力のテスト用スイッチで、隣同士を手動で逆相になるようにスイッチをパチパチします。真ん中のブレッドボードの1枚づつが1タームに相当。各タームの下の部分のトランジスタ4個相当(実トランジスタは2個しか刺さっていない)がAND平面、ほぼ中央にNMOSインバータがあり、上の2トランジスタがOR平面となります。右が出力を知らせるLED。点灯したらPLAの出力が1に相当。

まあ、思ったような動作は致しておるようです。

ここまでNMOS(もどき)とは言え、スタティックな回路ばかりで組み立てたので、そろそろダイナミックな回路へ行きたい。でもそのためにはクロック回路をば、まず作らないと。