当然、案の定、前回の醜い抵抗挿入に関してAraha氏からお叱りのメールがありました。「もっとよく考えよ」と。ごもっとも!でもね、これにもね、コロナの影が落ちております(言い訳だ)。コロナとGWが重なり電子部品の通販サイトがかなり混み合っているみたいなので、「忖度」して発注を控えさせていただいた、というのが一つ。本当か?

まず、Araha氏のご指摘の第一、

大きな電流が流れるといってもスイッチングの一瞬、パスコンでも入れよ

と。はい、パスコン入れます、ハンダづけした回路には。パスコンでも入れて消費電流を平らかにしてしまえば、醜い抵抗などいれなくても正常に動作するであろう、とのご指摘。特にトラ技の付録基板のCMOS回路どおりであれば、その通りなのであります。MOS-FETそのもののオン抵抗は小と言えども、定常的に流れる電流はゼロ。心配するようなことはないでしょう。また、トラ技の特集のように、

ディスクリート素子でコンピュータを作ることで論理回路を学ぶ

という目的であれば、動作する回路が作れればOKでしょう。ところが、トラ技記事に触発(?)されたとは言え、私の目的は、

古き良き時代(?)のN-MOS回路(もどき)を愛でる

ことであって、論理回路を学ぶ気も、コンピュータを作る気もありません(そういえば、昔、作っていた気がしますが)。どちらかというと、古代の回路の「テク」をそんなこともあったな~とノスタルジーに浸りたい、というもの。よって回路として速く動作することなどお構いなしに、回路動作の模擬そのものが目的になってしまっているのであります。

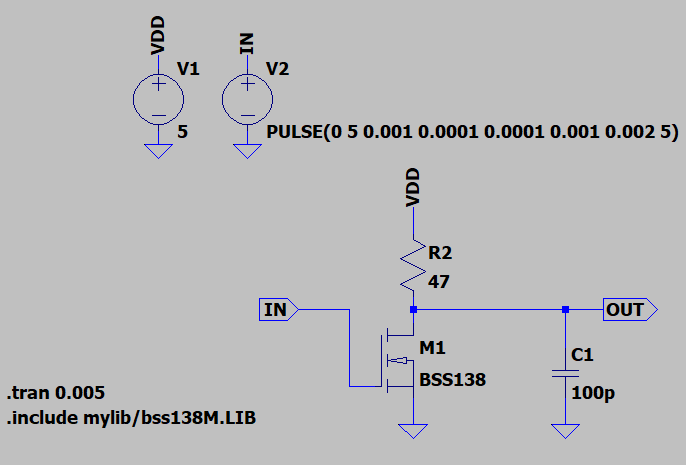

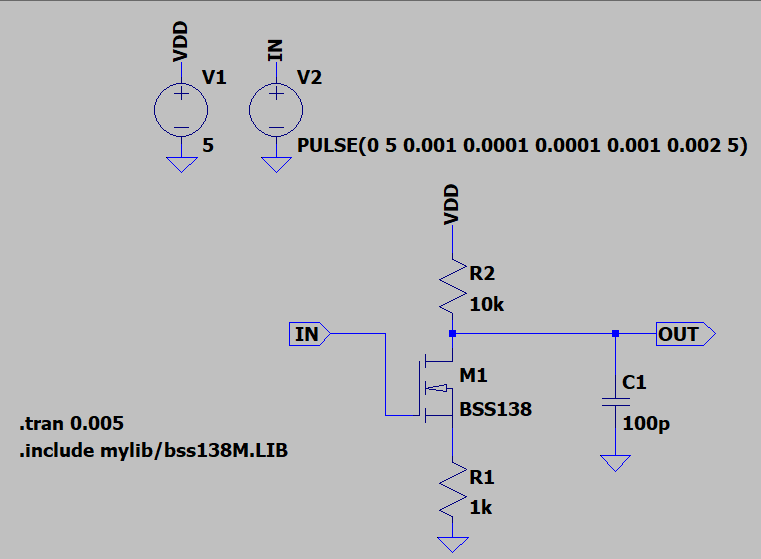

さて、考えている「なんちゃって」N-MOS回路の一例としてインバータをあげます。本来のN-MOS回路では、スイッチングの主体となるエンハンスメント型のNMOSトランジスタはLOWに引っ張り下げる方だけを担当し、HIGHに吊り上げるのはデプレッション型のNMOSトランジスタの役割でした。CMOSではPチャネルトランジスタで行っている電流の流し出しをNチャン・デプレッショントランジスタがやっているわけです。デプレッショントランジスタはトランジスタといいつつ、その役割はプルアップ抵抗みたいなものです。Pチャネルトランジスタのように能動的にスイッチをON/OFFしているわけではありませぬ。ただ残念なことに、デスクリートのデプレッショントランジスタなど影も形もありませぬ。手元にあるNチャネル・トランジスタは、連休前に仕入れた

BSS138が75個(数十個はすでにつかってしまった)

のみ。よって、デプレッショントランジスタは抵抗で代替することに即決。こんな感じ。

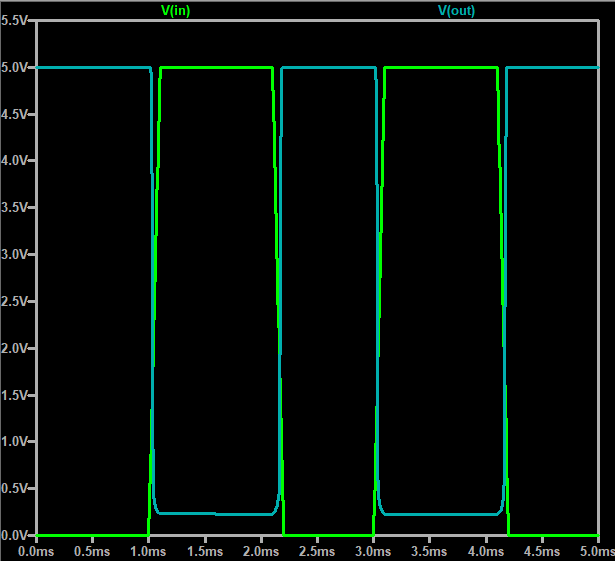

たったNMOS1トランジスタの上記の回路ですが、ちゃんとインバータとして動作します。下を御覧じろ。黄緑が入力、青緑が出力です。

そうです、NMOS回路は、CMOS回路に比べたらトランジスタ数が約半分になってしまうのです。デプレッション・トランジスタなど単なるプルアップ抵抗のようなものなので、昔のNMOS回路のレイアウトでは、「ゲート本体」と飛び離れた「空いている」場所にちょこんとついているようなことがよくありました。実際、半導体業界で自動レイアウトが本格的に使われたのはCMOS以降と認識しています。CMOS回路はPとNの両方のトランジスタに同じ入力信号を入れないとならないので、ゲートは1箇所にまとめておきたい感じになります。その点、NMOS回路では、一本の信号線に複数のプルアップやプルダウンパスがつながっている感じになるので、当時の手動レイアウトと相まって

ファンタジー

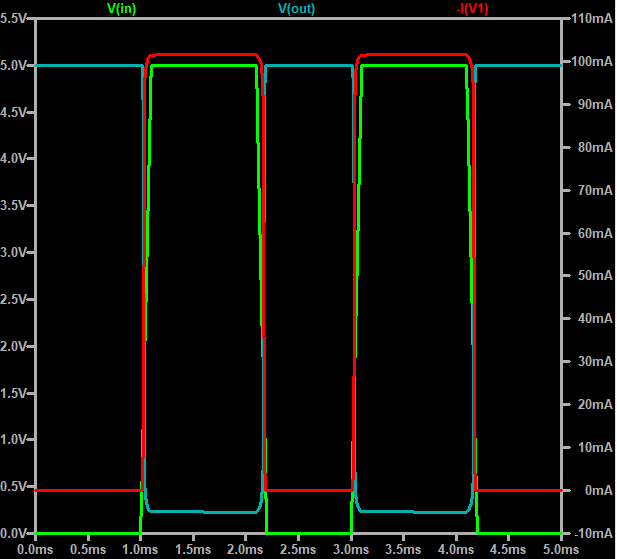

が成立していました。意外なところに回路が隠れていたりして。閑話休題、上記の波形に赤の消費電流を重ね合わせてみましょう。こんな感じ。

ほえほえ、VoutにLOWを出している間、100mAも流れています。そうです、

NMOS回路ではLOW出力のときにDC電流が流れる

のであります。でもね、上の回路を見ると、プルアップに47Ωとかとても小さい値を置いているからだ。これのせいだろ~。プルアップ抵抗を1kΩとかにすれば良いじゃん。「その通り」ではあるのです。しかし、いくつかの点を考慮する必要があります。

- LOW出力電圧は、プルアップ抵抗とNMOSのオン抵抗の抵抗分割で決まる

- 論理回路の場合、出力は次段のNMOSゲートに印加されるが、LOW電圧は「確実」にそのゲートをOFF状態にできるほど低くないとならない。

- 一方、HIGH出力電圧は、プルアップ抵抗により電源電圧まで振れるので、次段のNMOSトランジスタをON状態にするのに抵抗値の制限自体はないが、ON状態になるまでの時間は、NMOSゲートのキャパシタンスをチャージしてスレッショルド以上に持ち上げるまでにかかる時間時間であり、その抵抗値により決まる

最初の回路でみてみれば、BSS138のオン抵抗は数Ω、プルアップ抵抗は47Ωで、BSS138のスレッショルド電圧はあてにならないSPICEパラメータからすると1V(本当か?もっと実際には高いのではないかと疑う)なので、1、2の点はOK。ただし、3を考慮するとHIGH出力時に使える流し出しの電流は、LOW出力時に引ける電流より10分の1くらい小さいことがわかります。ただ、次段のNMOSのスレッショルド電圧は1V付近と低いので、大きな電流で5Vから1Vまで引き下げるのと、小さな電流で0.5V以下から1Vまで引き上げるのはそれほど時間に差がないでしょう。ところが、プルアップ抵抗に1kΩ採用すると、このバランスが崩れます。多分、LOW出力が伝わる方が、HIGH出力より圧倒的に速くなるでしょう。論理回路の場合、0の出力と1の出力の速さに差がありすぎると使い難い、と思います。よって、NMOSトランジスタがONするときに流れる電流を抑えるためにプルアップ抵抗の抵抗値を大にするなら、トランジスタ側がONするときの抵抗値もそれに合わせて大きくしたいです。Araha氏はおっしゃいます。

トランジスタを直列にスタックすればよいだろ

その通り。いただきました。実験はいたします。MOSトランジスタの駆動能力が足らないときに並列に並べるというやり方は普通ですが、直列にするというのは「逆転」の発想です。ただし、乏しい電源の「予算」(お金も乏しいですが)内で許容できる電流程度にできるオン抵抗値を考えると

BSS138を10個くらいは最低

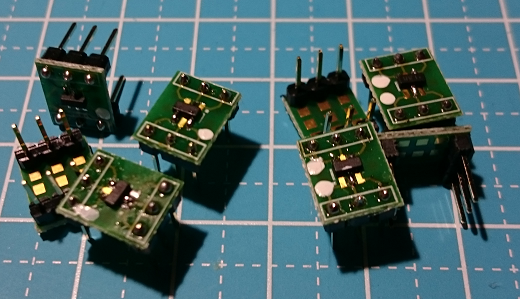

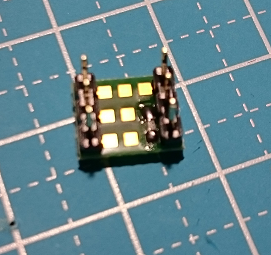

スタックしたくなります。もしかするともっと。そこで立ちはだかるのが、部品の壁です。ぶっちゃけ、BSS138は75個しか買ってないし、アイキャチ画像にした、SOT23をブレッドボードに刺さるようにできる変換基板は20枚しか買ってないし、です。回路的には「1個」分のトランジスタに何十個も使うのは

GW明けに部品屋さんが空いてきて、部品を追加発注できるまでは

遠慮したい。まさにコロナの遠い影響?実際には変換基板がいくら小さいとは言え、小さなブレッドボードに10個以上並べるのは辛そうなので、ユニバーサルボード上に手半田するのがとても辛い、というサイズと根性の問題が大きいのですがね。そこで以下の「醜い」回路となるのであります。

こちらのシミュレーション結果、最初から赤の電流を追加したもの(Voutは青になっています)はこちら。

ちゃんと、インバータとして動作しておりますし、DC電流流れるといっても450μAくらい。余裕(本当か?)。

しかし、トランジスタの下の抵抗が如何にも醜い。その対策(単に見かけだけの)はちゃんと考えておりましたよ、これです。SOT23変換基板の裏面。端子に対応するランドが置いてあるのです。右下のランドに1206の抵抗がハンダしてあるの見えますか?(例のリール買いの部品、在庫約5000個!)

醜い1kΩの抵抗を裏面に隠してしまいました。まったく同じCMOSインバータの回路(上下に抵抗付き)を、トラ技5月号付録基板と、細工したSOT23変換基板で並べるとこんな感じ。臭い物に蓋。

ファンシーなNMOS(もどき)回路は、これらの小さい基板を「駆使」して構成してみる予定です。でも全部は辛いので、必要な周辺部分は、トラ技付録基板のCMOS回路をそのまま流用させてもらうという折衷案なのでありますが。