前々回8080のクロックはメンドクセー2相ノンオーバラップクロックだと書きました。当時は8224という「8080専用クロックジェネレータ」が存在。それを使えばOK。しかし8224が出るまでは皆さん自分で作っていた筈。今回はそんな古の時代を偲びつつクロック波形もどきを作ってみたいと思います。現物の8080は無いのだけど。

8224

今回8224のご尊顔を拝し奉らんと検索したところ『itofamily.com』様の以下のページに行き当たりました。

怒涛のコレクションであります。本家インテル製8224だけでなく、他社製の8224も網羅。すごいです。一見に値します。8224は『ほぼほぼ8080の専用』の周辺チップなので、8080人気にあやかりたかった会社がなんと沢山いたことか。なお、8224でのノンオーバラップクロックの生成方法は以下でやっているような「成り行きの遅延まかせ」ではなく、もっとロジカルみたいっす。それ以外のお仕事もいろいろしていたらしいし。

2相ノンオーバラップクロックの生成方法

古の「遅延で削る」スタイルの2相ノンオーバラップクロックの生成方法についても検索したところ、あろうことが当サイトの古いページが上位にヒットしてしまいました。忘却力です。そういえば昔やったことがある気がする。。。

昔の記事を改めて読んでみると単体のMOSFETを駆使して回路を作っているのでとっても大変そうでした。2度とやらんな。MOSFETで「遊ぶ」記事なので仕方ないけれども。それに発生しているのは2相ノンオーバラップではあるのですが、8080へ与える2相ノンオーバラップクロックよりずっと遅くで隙間もデカすぎです。

今回は

-

- その辺に転がっている筈の標準ロジックIC2個で回路を作る

- 8080のスペックに適合する雰囲気を醸す

という目標であります。ただし、回路の動作は上記の記事と同じです。

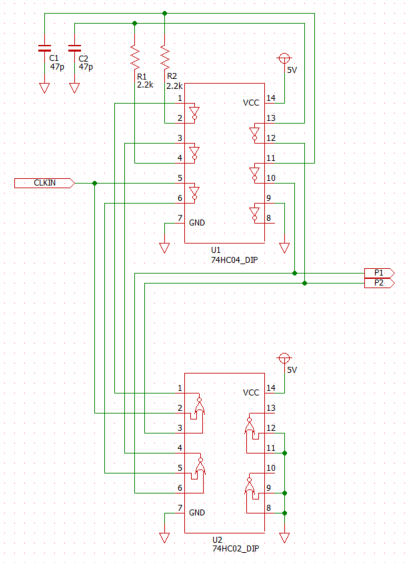

今回実験の回路

今回実験の回路が以下に。わざわざICイメージの部品を並べたのは、後でブレッドボードを配線するときにその通りに配線したかったからです。忘却力の年寄はよく間違うんだ、配線。目もショボショボだし。

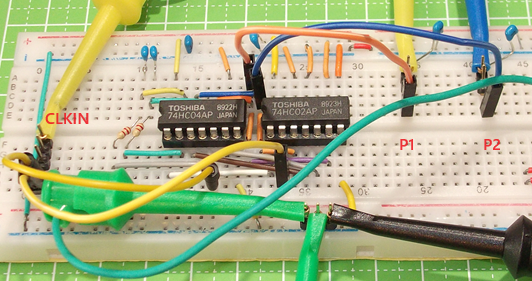

ブレッドボード上で実験

上記の回路どおりに配線したブレッドボードが以下に。配線込み入っているので斜め配線もあり、また空中のジャンパもあり、やっつけ仕事だな。

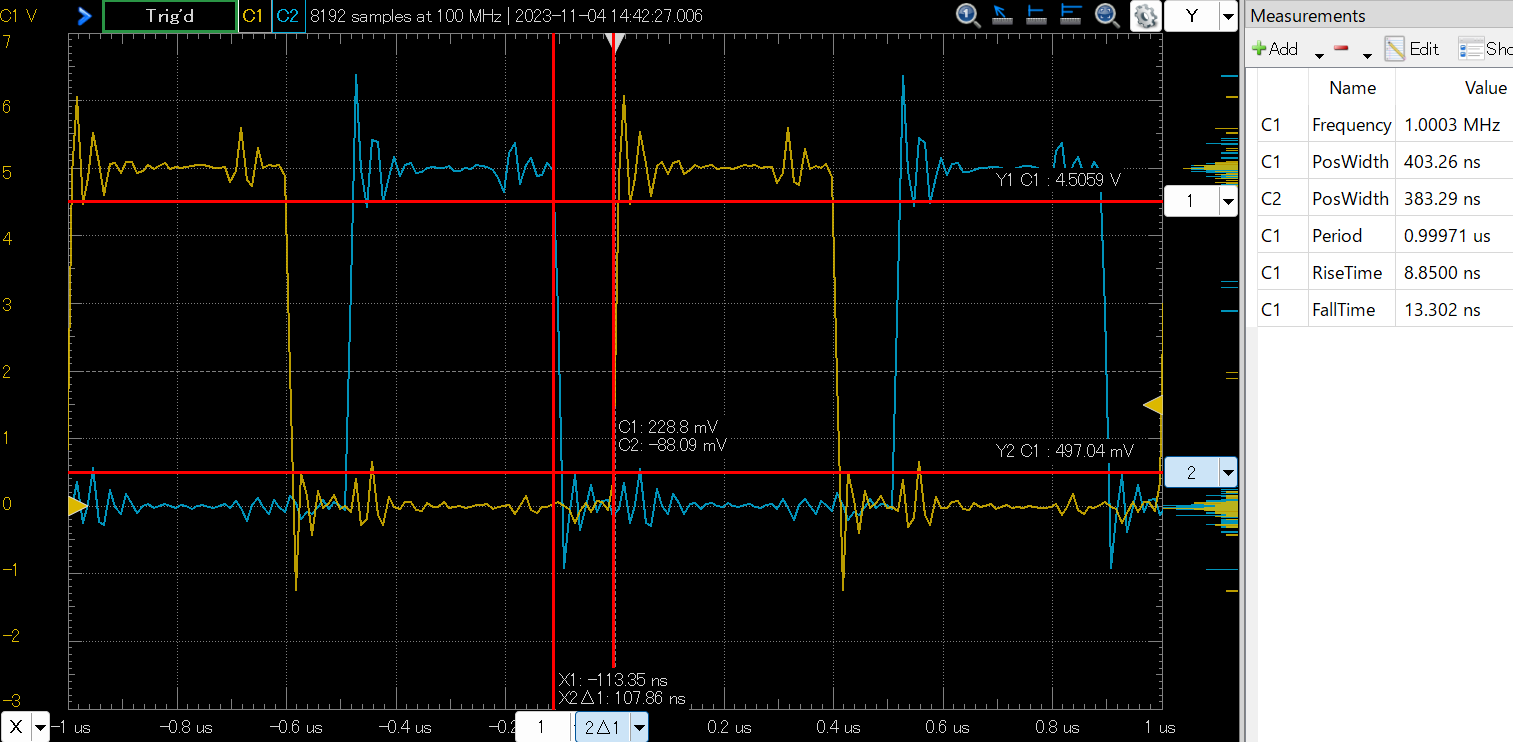

上記回路を動作させたときの波形が以下に。黄色C1がP1(Phase1)、青色C2がP2(Phase2)のつもりです。オーバーシュート、アンダーシュートが酷いけれども御勘弁(手抜き。)そこは無視して波形を見てくだされ。

まず、CLKINには1MHz、5Vpp(0~5V)の信号与えてます。当然周波数は1MHzとな。8080的には2MHzでもOKだった筈なのでここはクリア。

クロックのライズタイム、フォールライムは50nsまで良いみたい。上記は規格上はOKだけれど、ちょっと頑張りすぎかも。もっとゆるゆると上げ下げしてオーバシュート、アンダーシュートを低減しないと。

P1、P2のパルス幅の最小値はP2の方がきつくて最低220nsみたいです。今回は1MHzだし楽勝。

さて、肝心の「ノンオーバラップ」部分はというと、P2の立下りからP1の立ち上がりの間の部分の方の規定がきつくて70nsらしいです。上記の画面キャプチャは見ずらいですが100ns以上とれている気がするのでOKそう。

波形が暴れているのを何とかすれば「隙間」のところのスペックとしては8080に入力できそうか?ホントか?