生成AIしてますか?バリバリ使ってらっしゃるじゃないかと思います。頭の固い年寄はサッパリです。でもまあ生成AIのプロンプトにはたまにお世話になっております。便利。噂ではPythonなどのコードなど一撃で書いてくれるみたい。メジャーな言語はね。マイナーなのはどうだろう?例えばVerilogということで今回やってみました。

※最近、使えるようになったGoogle様の生成AI、Gemini(無料プランだけれども)を使ってコードを生成してもらっています。

ハードウエア記述(RTL)言語Verilog

「デジタルな」ハードウエアを設計されている人々にはお馴染みのVerilogはRTL(Register Transfer Level)と呼ばれる範疇の言語です。1980年代から論理回路の記述に使われておる言語です。今でもVerilogとVHDLの2言語が双璧。

ひとたびVerilogで記述すれば、ハードウエアの論理シミュレーションは勿論、論理合成ソフトウエアを介して、FPGAやASICやらの現物論理回路にマッピングすることも可能。

ただし、ハードウエアのための言語なので、「ソフトより」のプログラマの皆さまにおかれましては、お馴染みでないのでないかと。ざっくりしたことを言えばbegin~endが使われていることもあり、「工業Pascalか、Modula」的な雰囲気です(なつかし~。個人の感想です。)ただし、上から下へ流れるソフトのための言語と決定的に異なるのは、ハードウエアの特性から「同時に代入が起こる」書き方が主になることです。ソフトならAに代入する行の次にBに代入する行が書いてあれば、Aが先、Bが後ですが、Verilogの場合、代入は同時に起こる(書き方が普通、ソフト的な書き方も可だがハード記述ではあまり使わん)ってこってす。

そんなマイナー?言語のVerilogのコードをGemini様に書いていただきましたぜ。

第1のターゲット、10進バイナリカウンタ

最初のターゲットにいたしましたのは、バイナリカウンタであります。

-

- クロックが入力される度に+1される(カウンタ)

- 0から始まって(0初期化はリセット信号による)最大カウントまで2進数で数えたら0に戻る

デジタル・ハードウエアのHello World的なやつ。今回 Gemini様のプロンプトにお願いしてみたのは以下とおりです(日本語デス。)

Verilogを使用して、4ビットバイナリカウンタを作製してください。

Geminiの生成したコードをXilinx Vivadoへ入力

別シリーズで、Digilent社のCMOD S7という小型FPGAボードを使用中です。このボードにはXilinx(AMD)社のFPGA(Field Programmable Gate Array)スパルタン7というチップが搭載されており、任意のロジックを実装可能です。CMOD S7は廉価版のボードなので搭載されているFPGAもささやかなサイズのものなのですが、それでも簡単な32ビットCPUくらいなら実装可能であります。

FPGAにロジックを書き込むにはXilinx社のVivadoというツールを使います。Verilogソースを論理合成してFPGAに書き込むだけでなく、正しく動作しているか否かシミュレーションすることも可能です。

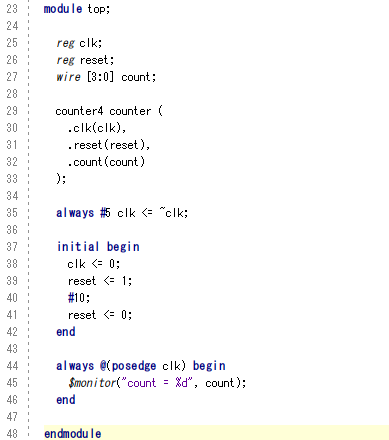

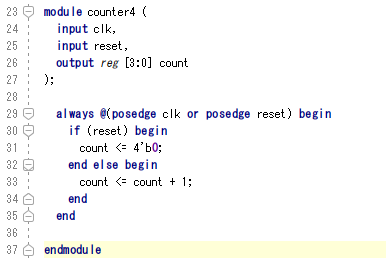

今回はGeminiが出力してくれたVerilogソースに一切の手を加えることなく、Vivadoに入力してみました。まずは、4ビットバイナリカウンタ本体から。

ぜんぜん違和感ないコードです。Verilog不得意の老人はGemini様にお願いしたくなりましたぜ。

ハードウエアのシミュレーションをする場合、ハード本体のコードのみでは完結せず、そのハードを駆動して結果を出力(あるいはチェック)するためのテストベンチといわれるコードも必要です。感動したことにGemini様は、何も言わないのに、テストベンチ相当のコードも同時に作成してくれました。こんな感じ。

シミュレーションしてみる

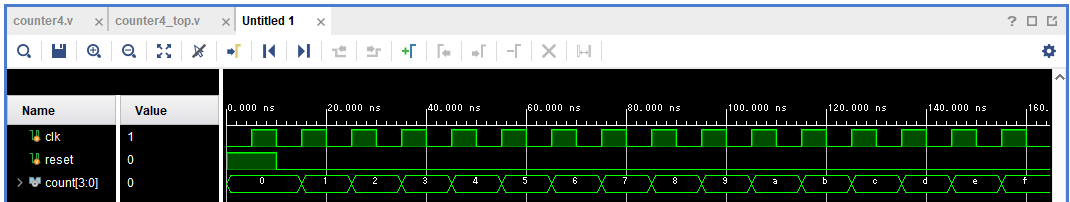

Gemini出力そのままの上記コードで「ビヘイビア」なシミュレーション(ハードに実装後に問題になる物理的な遅延などを加味せず、論理的な挙動のみを検証するシミュレーション)を行ってみました。その様子が以下に。

動いとるがや。ちゃんとバイナリカウンタしているじゃん。。。

後、制約ファイル(Verilogソース上の信号名とFPGAのチップ上の具体的な信号端子を紐づけたりするためのファイル)作成すれば、多分FPGA上への実装はできそう。流石だな、Gemini。