生成AIしてますか?頭の固い年寄はサッパリなので練習中です。今回はGoogle GeminiにBCDデコーダを設計してもらいました。標準ロジック 74HC42 相当の動作をする回路を想定。前回のバイナリカウンタは生成されたVerilogソースそのままでシミュレーションOKでしたが、今回は多少変更が必要でした。

※最近、使えるようになったGoogle様の生成AI、Gemini(無料プランだけれども)を使ってコードを生成してもらっています。

BCDデコーダ

BCDデコーダは、BCD(バイナリ・コーデッド・デシマル、2進化10進数)をデコードするものです。7セグメントLEDを駆動するときに「7セグ」タイプのBCDデコーダが使用されることが多いです。その辺の事情をGoogle Gemini様はお見通しみたいで、何も言わずにBCDデコーダを作ってとお願いすると7セグ用のVerilogソースを生成してくれました。まあ、7セグ用の回路を修正しても目論見の回路は直ぐできるのだけれど。

今回は、標準のロジックIC

と同等のデコーダを作製したいと思います。別シリーズでチップセレクト信号の生成に使っていたりするもの。BCD-to-decimalデコーダね。なお、また別なシリーズで、手作業で作成したVerilogソースをFPGA(Xilinx Spartan7)上に実装して動作確認までしてます。今回はGeminiに作成してもらったVerilogソースを前回同様Xilinx Vivado環境でシミュレーションして動作確認したいとおもいます。

プロンプトへの入力

今回はこんな感じっす。

Verilogを使って、10進BCDデコーダを設計して

何も指定しないと7セグ用のデコーダを生成しようとするみたい。そこであえて「10進」と指定してみましたぜ。4ビット入力と書こうかとも思ったのですが、Gemini様がBCDの「1桁」は4ビットだと分かっていらっしゃるみたいだったので省略。

最初に生成された結果が「ぱっと見もっともな感じがするけど、いただけないやつ」だったので、今回は3案だしてもらいました。結果はこんな感じ。

-

- 第1案、いただけない感じだったので却下。

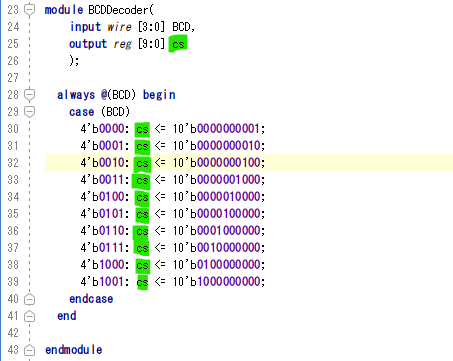

- 第2案、OKな感じだったので、本体ソースはこれを採用。

- 第3案、第一案の焼き直し的なヤツなので却下。ただし、第3案にはテストベンチ相当のモジュールが別途生成されていたのでテストベンチ部分はこれを流用。

なお、いただけない感じとかOKな感じとかは個人の感想ですが、多分いただけない感じのやつは思ったような動作しないデス。

Vivado環境でシミュレーションを試みた結果

-

- 問題点、キーワード

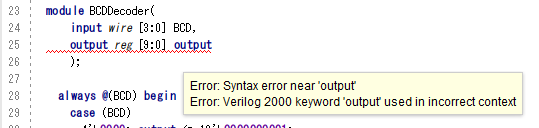

第2案の回路構成自体は良さげ(当方の意図に近い)だったのですが、ソース冒頭にエラーが含まれてました。こんな感じ。

モジュールの出力信号名に output とか名前をつけているのがエラーの原因でした。Vivadoのエディタがエラーを見つけて上記のように理由も提示してくれるので、変更はお楽。ううむ、案1、案2ではフツーに使えるお名前が信号名につけられていたのに、案2だけキーワード含んでました。帯に短し襷に長しってことかい。ここは output を cs (チップセレクトのつもり)とお名前変更。修正後のソースが以下に(緑のマーカ部が修正したところ。)

-

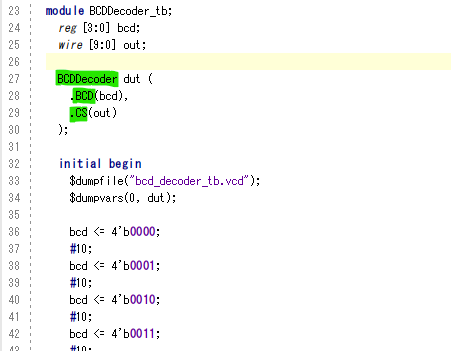

- テストベンチ・ファイルとの整合性

第2案のソースを第3案のテストベンチと組み合わせようとしています。Gemini様のソースは案の中では整合性がとれているお名前みたい。しかし案をまたぐ整合性はないようなので、信号名の変更は必須でした。それに、第2案のモジュール本体ソースに手修正を入れてしまってもいます。結局、テストベンチ部分にも修正が必要。テストベンチのソース先頭部分はこんな感じ(緑のマーカ部が修正したところ。)

-

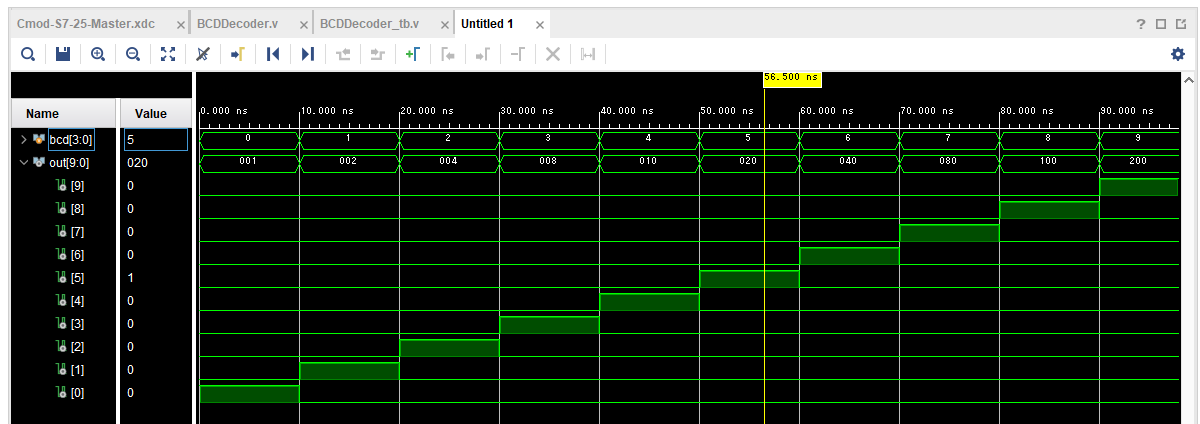

- シミュレーション結果

BCDをデコードしておるね。ただ74HC42はローアクティブ、Gemini様の結果はハイアクティブ。そこは言ってなかったな。。。