「なんちゃってな図」と「ほんわかした説明(数式なし)」により分かった気になるのか?というシリーズ第4回です。前回は「シリコンウエファ」を遠くから眺めてみました。今回はシリコンウエファの上に製造された半導体製品(IC)に、もそっと近づいて見ていきます。まあね、ウエファを切っただけではただの石。外部と接続せんと。

回路はウエファの片面よ

前回のおさらいになりますが、「回路」はウエファの片面の表面に形成されます。数十層くらいの各種の「レイヤ」を積み重ねて回路を作ることになるのですが各レイヤは極めて薄いので、回路が存在するのはウエファの厚みに比べたらごく表面の薄い層の中です。ウエファ自体の厚みはウエファ・サイズにもよりますが数百マイクロメートルです。しかし最近のモダーンな小型パッケージからするとその厚みすら「許しがたい」ので、回路が無い側の裏面を削ってウエファを薄くしてからパッケージに封入するのが普通でないかと。

チップを覆う膜、パシーベション

さて、表面にある回路は「生もの」ということになってます。なにもしないと「腐る」らしいです、例えだけれども。昔、実験室で「パシベーション無の裸のウエファ」上の回路をデバッグしていたご同僚が、数週間でウエファが腐ったなどとブーたれてました。何もしないとそんなもんらしいです。

第1回などで見たとおり超微妙な濃度の不純物をコントロールしているのが半導体製品なので、外部からナトリウムイオンなどやってくるとすぐに特性が変わり動作しなくなってしまいます。ちなみに人間の汗などはナトリウムの宝庫だと。そして、一般的なプラスチックパッケージ、水など通さないように感じられますが、半導体の微妙な「濃度感覚」だと、水などじゃじゃ漏れだそうな。知らんけど。

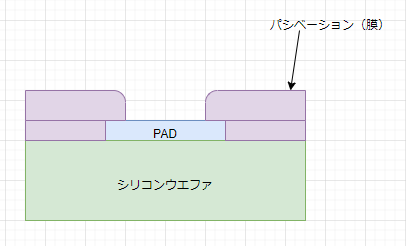

そのため、チップ表面を「パシベーション(膜)」という強度が高く、不純物など通さぬ、そして勿論電気を通さぬ絶縁膜で覆うことが行われます。材質としてはSiN(窒化シリコン)が多いみたいです。

ただし完璧にパシベーション膜を形成してしまうと信号も電源、グラウンドも接続できません。そのため、それを接続するための金属部分であるPAD(ボンディング・パッド)の中央部だけパシベーションに穴を開けることになってます。こんな感じ。

チップを遠くから眺めてみると

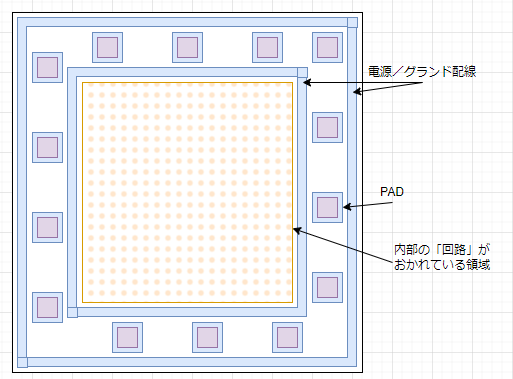

最近のチップのプロセスはxxナノメートルみたいな微細なことを言ってます(どこが何ナノかは言わんけど。)当然、虫眼鏡などでは見えない幅ね。学校で生物観察に使う光学顕微鏡でも無理でしょう。しかし、多くのチップで虫眼鏡くらいの倍率でハッキリ見える構造があります。目のいい人なら裸眼でも分かるでしょう(老眼の年寄には無理っすけど。)こんな感じ。

真ん中のオレンジドット部分が、「微細な」回路が形成されている部分です。ここに、その製造プロセスでもっとも細かいパターンを使って実際の回路が形成されています。大昔は光学顕微鏡で1個1個のトランジスタを十分識別できたのですが、最近の奴らは微細になっただけでなく、配線の金属層の数がとても多く積み重なっているので、その層の一番下にあるトランジスタなどは隠れてしまってます。

しかし一般的なICの場合外側に、外部回路と接続するための端子(PAD)が設けられているのが見えると思います。またその周りを「ぶっとい」配線(といったって数十~数百マイクロメートル幅)が取り巻いているのも見えるでしょう。そいつらは、電源、グランドの配線です。

内部の回路のトランジスタはどんどん縮小されていきますが、外部と接続する部分は、5V電源で1端子あたり2mAは流してね、とか電気的な制約があります。細い配線では外部とのインタフェースに必要な電流を流せないので、必然的に「目に見える」ような太さになるのですな。泣く子と電流には勝てぬと。違うか。また、外部との間の接続は機械的な配線になるので、これまたそんなに小さくはできませぬ。

2流派、上向き、下向き

さてチップを外部(といってもパッケージの内部の端子、あるいはボード直付けの場合はボード上の端子)と接続するにあたっては2流派ありです。上向きと下向きっす。

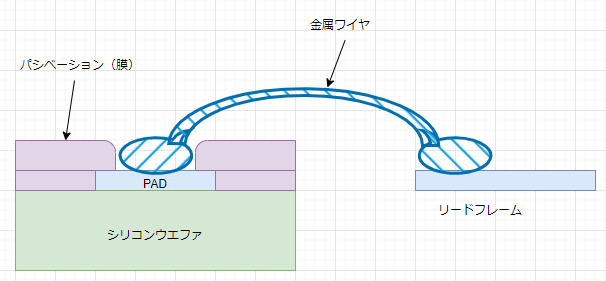

半導体チップは真ん中に上向きに置かれていて、パッシベーションに開けてある穴に向かって金属ワイヤ(ボンディング・ワイヤ)が接続されています。パッケージやチップによりますが、古くは金やアルミニウム、最近では銅に特殊な被覆を被せたものが多くなっているみたいです。金高いからなあ。

「ボンダー」という機械でチップ側とリードフレームを結線していくのですが、ちょっとみ、すごい速さで接続される感じです。でも端子数が多いとそれなり。昔、後工程出身のドイツ人が、ボンダーのあの匂いが忘れられんぜ、とか言っていたのを思い出しました。私は後工程の人でないのでよくわかりません。

ボンダーの機械の先端部分がすごい速さで行ったり来たりするので、それがお隣のワイヤに引っかかったりしないように、PADとリードフレーム間の結線を考えてPAD位置をきめたり、リードフレームを選択する、などということも必要です。

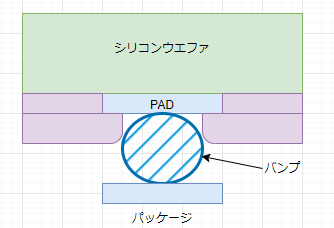

シリコンのチップを表裏ひっくり返して、PADが下向きになるようにして、下側にあるパッケージ内の端子と接続します。間にはバンプなどと呼ばれるハンダ・ボールなどを挟んでです。まあ、実際にはいろいろ表面処理などムツカシーことがあるみたいですけど。

さてこちらの方が上向き派よりもPADの配置に自由度が高いことが分かるかと思います。上向きだとワイヤが空中を飛ぶので、どうしてもチップの端に一列にPADを並べる感じになります。一方、下向きであれば、チップの中央にPADを置いたって後はパッケージ次第。

今を去ること30有余年も前、チップの中央部に整然とPADを並べてあるだけでなく、PADの下に「アクティブな回路」を実装できる(圧力かけても下のトランジスタ構造などが潰れない)「C4フリップチップ実装」というのを見たときにはその過激さに驚きましたが、今は昔。

まあ、そんな過激でなくても、チップ・サイズ・パッケージ(CSP)とか小さい表面実装パッケージが主流になっているので、下向き派の勢力は絶賛拡大中かと思います。それでもDIPは電子工作の友だけれども。